## Synthesis of Digital Architectures

- Self-contained course

- no previous requirements beyond compulsory courses

- all material is described in these notes and during the lectures

#### Course materials will draw on several texts

- Giovanni De Micheli, "Synthesis and Optimization of Digital Circuits", McGraw-Hill, 1994

- A good description of most of the topics covered

- Also covers logic synthesis, not covered in this course

- Keshab K. Parhi, "VLSI Digital Signal Processing Systems", Wiley-Interscience, 1999

- · Useful for retiming, and a slightly different perspective

- Sabih H. Gerez, "Algorithms for VLSI Design Automation", Wiley, 1999.

- Useful for a general overview, and some details on floorplanning

M McFarland A Parker R Camposano "The High-Level Synthesis of

- M. McFarland, A. Parker, R. Camposano, "The High-Level Synthesis of Digital Systems", Proc. IEEE, Vol. 78, No. 2, Feb 1990

- R. Camposano, "From Behavior to Structure: High-Level Synthesis", IEEE Design & Test of Computers, October 1990.

1/8/2007

Introductory Lecture gac1

## Administrivia

- Approximately 20 1-hour lectures

- An assessed "mini project"

- small groups develop some synthesis software

- Course website

- http://cas.ee.ic.ac.uk/~gac1/Synthesis

- Room 903, gac1@ic.ac.uk

- Questions / discussion welcome, but please email first!

```

1/8/2007

```

Introductory Lecture

gac1

2

# What is Synthesis?

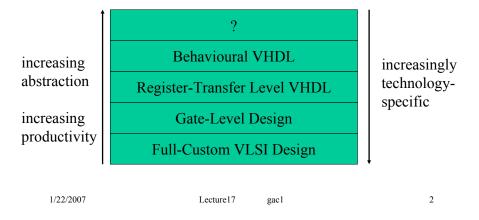

- Synthesis is the automatic mapping from a highlevel description to a low-level description

- gates to transistors

- AHDL or VHDL to gates

- Matlab to AHDL/VHDL (?)

- Synthesis is important because

- it raises designer productivity

- it allows design-space exploration

- it improves time-to-market

- it is a very big industry

- Synthesis is also a fun real-world application of some nice "game-like" parts of mathematics

1/8/2007

3

## What is architectural synthesis?

- Current synthesis comes in two main "flavours", depending on what is the input description and what is the output description

- logic synthesis

- given Boolean equations, map them into gates

- architectural ("high-level") synthesis

- given a description of circuit behaviour, create an architecture

- This course will give you a good understanding of architectural synthesis

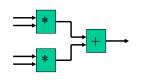

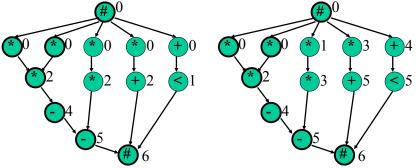

## **Example: Architectural Synthesis**

- Problem:

- create a circuit capable of implementing the behaviour "y[n] := a[n] \* b[n] + c[n] \* d[n]"

- Possible solutions:

(a) fast, big one result per cycle

1/8/2007

(b) slower, smaller (?) one result per 2 cycles

gac1

## **Course Syllabus**

- · Introduction to architectural synthesis

- scheduling

- when should I execute each operation?

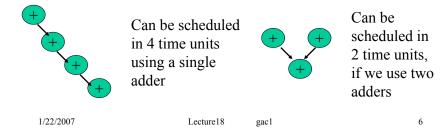

- resource allocation and binding

- how many of each computational unit should I use in my design, and which unit should do which task?

- area and performance estimation

- how big will my design be and how fast will it run?

- control unit synthesis

- how can I design the controller to tell each unit what it should be doing at each time?

```

1/8/2007

```

Introductory Lecture gac1

6

## Course Syllabus

Introductory graph theory and combinatorial optimization

Introductory Lecture

- what is a graph, and how can we use one?

- tractable and intractable problems

- longest path through a graph

- colouring graphs

- finding complete subgraphs

- integer linear programming

## Course Syllabus

- Scheduling algorithms

- As Soon As Possible / As Late As Possible

- list scheduling

- scheduling with integer linear programs

- affine loop scheduling

- retiming

- Resource sharing algorithms

- interval graph colouring

- register sharing

- resource sharing with integer linear programs

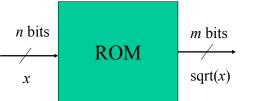

- Other topics

- function approximation

- floorplanning

- Subject perspectives and revision

gacl

7

## Introduction: Scheduling

- Part of a 4-lecture introduction

- Scheduling

- Resource binding

- Area and performance estimation

- Control unit synthesis

- This lecture covers

- The relationship between code and operations

- Data flow and control data flow graphs

- Modelling of conditionals and loops

- Resource constrained scheduling

- Scheduling with chaining

- Synchronization

1/12/2006

Lecture1 gac1

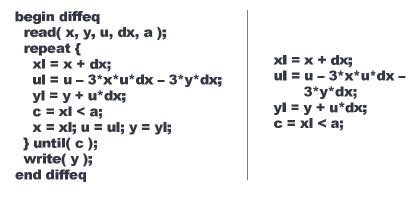

### **Example Code Fragment**

• Because we're engineers, we've written some code to solve a differential equation

```

1/12/2006

```

Lecture1 gac1

2

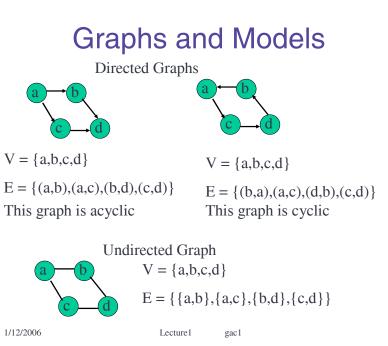

## Graphs and Models

- We want to express this code in a way that maintains the essential information

- · Graphs are useful for describing such models

- A graph G(V,E) is a pair (V,E), where V is a set and E is a binary relation on V.

- Elements of V are called vertices, elements of E are called edges.

- A graph can be undirected or directed depending on whether an edge is an unordered or ordered pair.

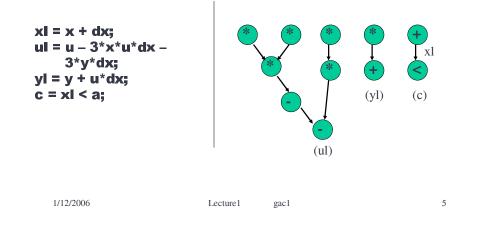

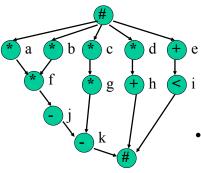

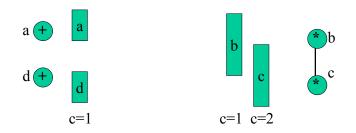

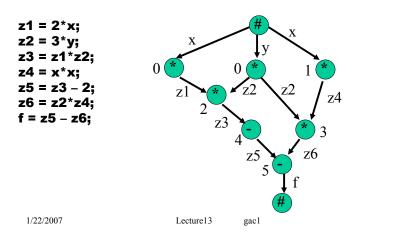

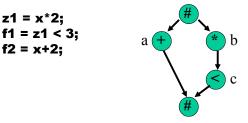

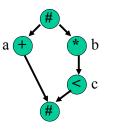

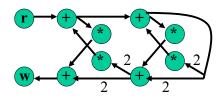

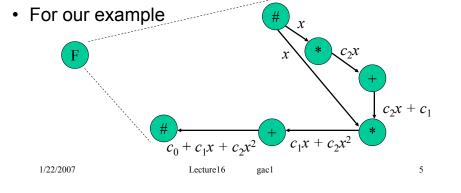

## **Data Flow Graphs**

• A data flow graph (DFG) represents the way in which data flows through a computation

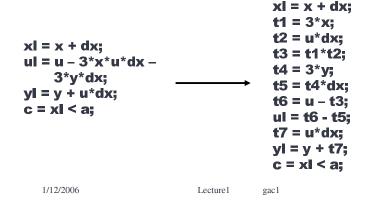

## Data Flow Graphs

• What we have done is to break up the algorithm so that we only use standard 2-input operators

## Data Flow Graphs and Compilation

- Splitting into basic operations is necessary for both hardware and software implementations

- For software, such a procedure is performed by the compiler. Each of the steps can be performed by an assembly instruction.

- Assuming 1 instruction per clock cycle, our code would take 11 cycles to execute. The data flow graph shows us how we can speed this up by taking advantage of *parallelism*

- The "value" of each edge into a node in the graph must be known before the computation described by the node can be performed

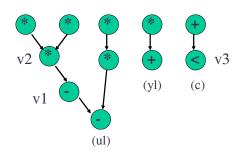

## Data Flow Graphs and Parallelism

- Operation v1 needs to know the result of operation v2 before it can proceed

- Operation v3 doesn't depend on v2 at all so we could do it at the same time if we had enough hardware to spare

1/12/2006

7

1/12/2006

Lecture1 gac1

8

## **Data Flow Graphs**

- Formally, a dataflow graph is a directed graph G(V,E) whose vertex set is in one-toone correspondence with the set of tasks, and whose edge set is in correspondence with the transfer of data from one task to another.

- Data flow graphs express the maximum parallelism available

- They do not allow us to express loops or conditionals

Lecture1

gac1

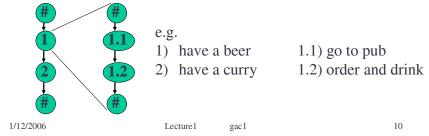

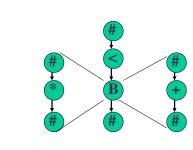

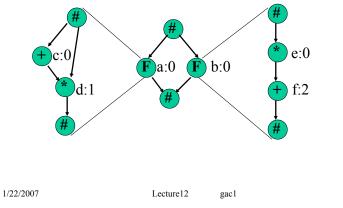

## **Control Data Flow Graphs**

- Structures which can also represent conditionals and loops are known as control data flow graphs (CDFGs)

- CDFGs are hierarchical graphs where each level of hierarchy is an acyclic DFG together with two additional nodes representing the start and end of the task

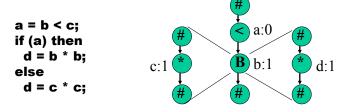

## Conditionals

Conditionals can be represented by introducing a task "B" (for branch) with two alternative expansions in the lower level of hierarchy

a = b < c; if (a) then d = b \* c; else d = b + c;

1/12/2006

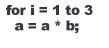

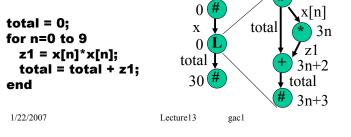

#### Loops

- Loops can be represented by introducing a task "L" (for loop)

- The "L" task tests the loop condition at each iteration, and does the necessary updates

gac1

11

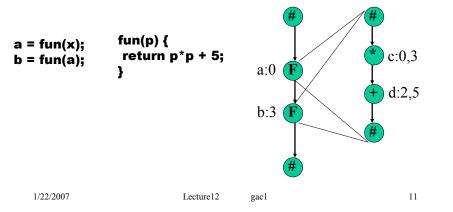

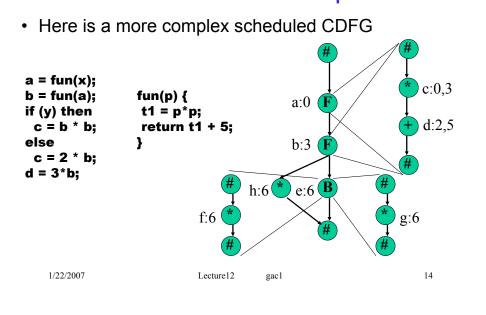

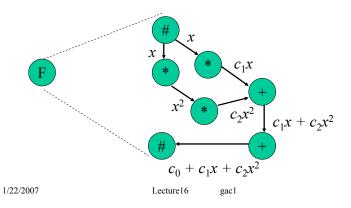

## **Function Calls**

- Function calls can be represented by introducing a task "F" (for function)

- The F-task calls the function body represented by the lower level in the hierarchy

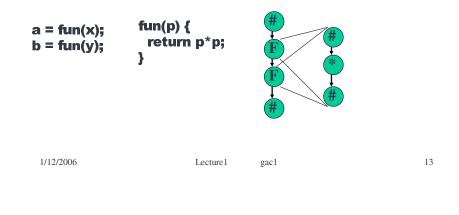

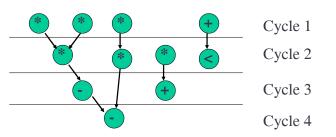

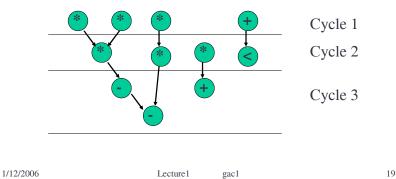

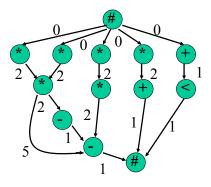

## A Simple Schedule

- What if we had unlimited hardware? How fast could we make our algorithm go?

- Let's assume that each operation takes one clock cycle

We need at least four clock cycles. This schedule requires at least 4 multipliers, 1 adder/subtractor, and one comparator

gac1

Lecture1

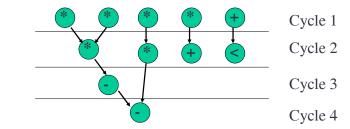

# Improving our schedule

• By shuffling around the execution of tasks, we can reduce the number of resources required

This schedule requires at least 3 multipliers, 1 adder/subtractor, and one comparator

## Schedule: Definition

- With each node v in the graph G(V,E), let us associate an execution time d(v)

- A schedule of this graph is a function S:V→N where for all edges (v<sub>1</sub>, v<sub>2</sub>) ∈ E, S(v<sub>2</sub>) ≥ S(v<sub>1</sub>) + d(v<sub>1</sub>)

- For each node *v*, S(*v*) denotes the start time of the relevant task

1/12/2006

gac1

## **Resource Constrained Schedules**

- Often our scheduling task consists of finding a schedule that will complete in a short time, subject to constraints on the amount of hardware available

- This is called "Resource Constrained Scheduling"

- Example: Schedule the differential equation code such that we need no more than:

- one multiplier, one adder/subtractor, one comparator

| 1/12/2006 | Lecture1 | gac1 | 17 | 1/12/2006 |

|-----------|----------|------|----|-----------|

|           |          |      |    |           |

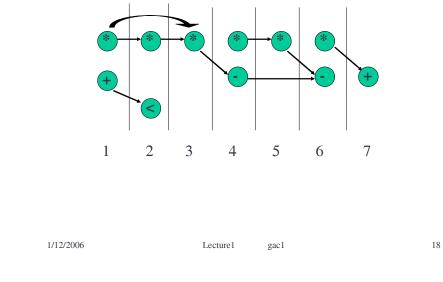

## **Resource Constrained Schedules**

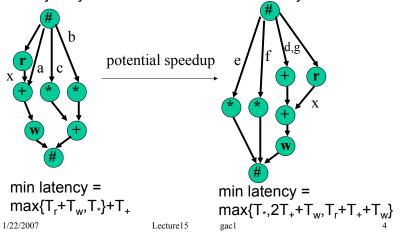

## Scheduling with Chaining

- So far, our basic unit of time has been the clock cycle.

- What if a subtraction only takes 0.5 clock cycles? We can do two subtractions in a single clock cycle.

## Scheduling with Chaining

- The advantages of chaining

- We can reduce the latency of our schedule

- The latency is the total number of clock cycles req'd

- We can avoid registers

- Each data transfer across a clock cycle needs a register to store temporary data

- The disadvantage of chaining

- We have to work with sub-clock cycle units

- Design of scheduling algorithms becomes more complex

1/12/2006

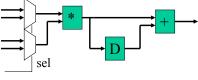

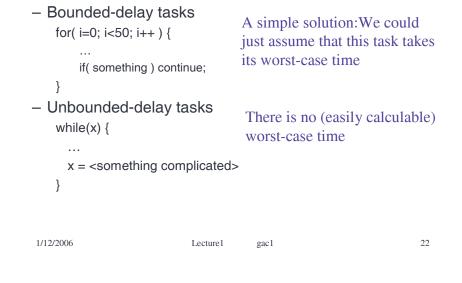

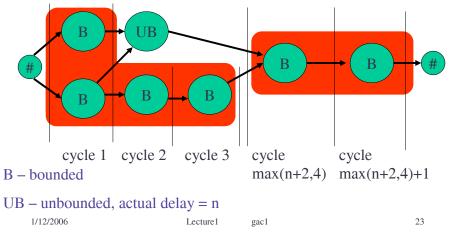

## Synchronization

- Multiplications and additions have predictable delays

- We can incorporate them into the scheduling model

- Some blocks do not, e.g. data-dependent iterations (while (a) { ... })

A hardware block with predictable delay

A hardware block with unpredictable delay

1/12/2006

21

→ done

## Synchronization

Tasks with unpredictable delay can be classified as

## Synchronization

• Methods are req'd to deal with unbounded tasks (they could also be applied to bounded tasks)

## Summary

- This lecture has covered

- The relationship between code and operations

- Data flow and control data flow graphs

- Modelling of conditionals and loops

- Resource constrained scheduling

- Scheduling with chaining

- Synchronization

- Later in the course, we will be exploring algorithms to do scheduling automatically

```

1/12/2006

```

## **Introduction: Binding**

- Part of a 4-lecture introduction

- Scheduling

- Resource binding

- Area and performance estimation

- Control unit synthesis

- This lecture covers

- Resources and resource types

- Resource sharing and binding

- Graph models of resource binding

- Conflict graphs

- Templates for architectural synthesis

- A complete worked problem

1/12/2006

Lecture2 gac1

#### Resources

- We refer to a piece of hardware that can perform a specific function as a "resource"

- e.g. a 16x16-bit multiplier, a PCI interface

- An operation could be performed on one of several resources

- e.g. a multiplication could be performed on one of two physically distinct multipliers

- e.g. an addition could be performed by a special-purpose adder, or an ALU.

- We are distinguishing here between the operation, and the resource that will execute that operation

```

1/12/2006

```

1/12/2006

Lecture2 gac1

2

# Resource Types

- The "type" of a resource denotes its ability to perform different operations

- A multiplier can do multiplications

- An adder can do additions

- An ALU can do comparisons and additions

- The resource type set R consists of all the different resource types we have available

- R = {multiplier, adder, ALU}

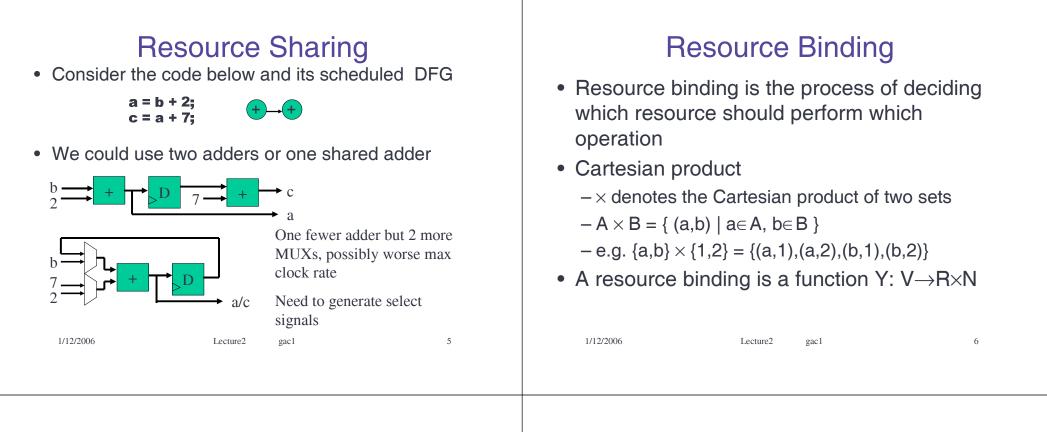

## **Resource Sharing**

- Just because we have *n* additions in an algorithm, we don't need *n* adders

- In traditional sequential processors, we use just a single adder to do all the additions in our program

- This is possible because we have scheduled them an adder is only used for one addition at one time

- Using the same resource to perform several different operations is "resource sharing"

- Advantage: can save area and peak power.

- Disadvantage: can make things slower and use more energy.

3

Lecture2 gac1

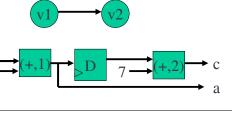

### **Resource Binding**

• Revisiting our example...

1/12/2006

7

gac1

Lecture2

## **Binding Graphs**

- A hypergraph extends the notion of a graph by allowing edges to be incident to any number of nodes

- We can represent a bound CDFG or DFG by a hypergraph G'(V,E∪E<sub>B</sub>)

$E = \{ (v1, v2) \}$  $E_B = \{ \{v1\}, \{v2\} \}$

$E = \{ (v1, v2) \}$  $E_{B} = \{ \{v1, v2\} \}$

Lecture2 gac1

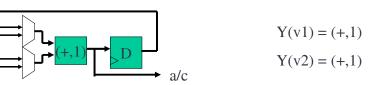

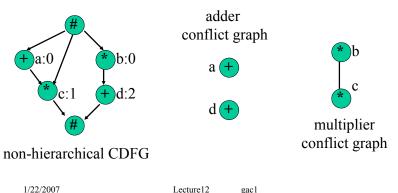

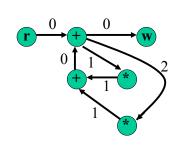

## **Conflict Graphs**

- Sometimes we must bind operations to different resources

- e.g. if they execute at the same time

- Such information can be represented using conflict graphs

- These have the same nodes as the corresponding DFG or CDFG.

- An edge corresponds to a conflict

- two nodes connected by an edge cannot be bound to the same resource

Lecture2

|    | LI: -T | Grap   |    |

|----|--------|--------|----|

| OD | пст    | ( ¬rar | ne |

|    | III UL | JUL    |    |

|    |        |        |    |

## **Conflict Graphs**

gac1

- In this example, the structure of the conflict graph is very simple

- two disjoint sets of nodes, each one fully connected within itself

- This is because all operations took a single cycle – with multicycle operations, conflict graphs become more interesting and important (a later lecture...)

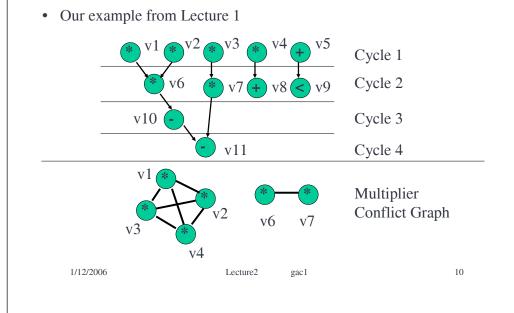

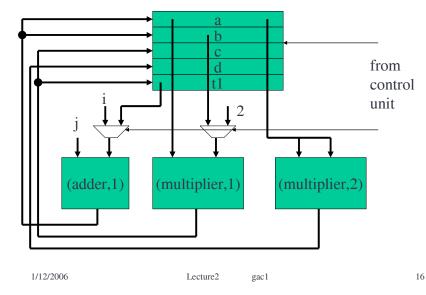

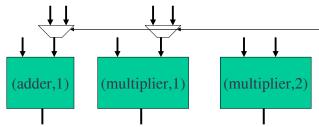

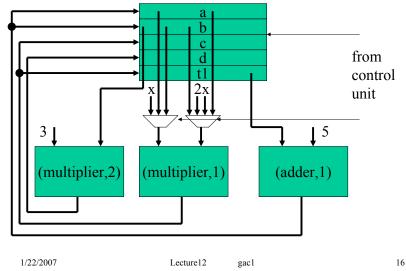

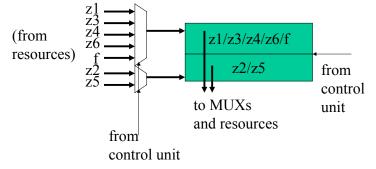

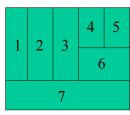

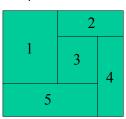

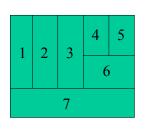

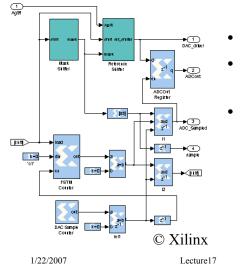

## **Architectural Templates**

- Once we have a schedule S and a resource binding Y, we know all we need to construct our circuit

- In order to do this, the synthesis tool needs to have a "template" in mind

- We will be working with register bus-based architectures: in one clock cycle

- values are read from registers, pass through multiplexers, and get steered to the right resource

- the operations are performed

- the results are written back into the registers

1/12/2006

11

9

1/12/2006

## **Architectural Templates**

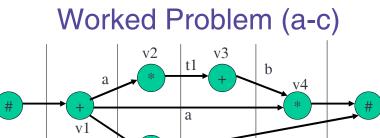

### Worked Problem

Consider the following code:

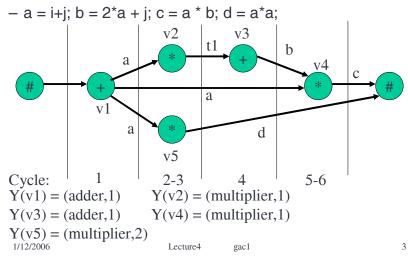

$-a = i+j; b = 2^*a + j; c = a^*b; d = a^*a;$

- (a) construct a CDFG for the code

- (b) schedule the graph so that each operation starts as soon as it can, assuming each multiplication takes two cycles and each addition takes one cycle

- (c) if you have the resource type set R = {adder, multiplier}, construct a resource binding for this example

- (d) draw the completed data-path

- (e) suggest a way you could save area

```

1/12/2006

```

Lecture2 gac1

$\mathbf{\Delta}$

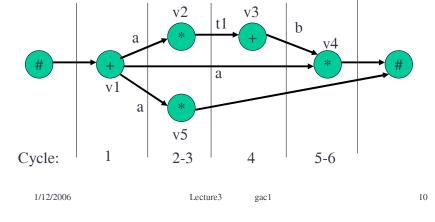

Y(v2) = (multiplier, 1)

Y(v4) = (multiplier, 1)

gac1

5-6

15

a

Cycle:

1/12/2006

Y(v1) = (adder, 1)

Y(v3) = (adder, 1)

Y(v5) = (multiplier, 2)

v5

2 - 3

Lecture2

## Worked Problem (d)

#### Worked Problem (e) Summary This lecture has covered Area could be saved by scheduling v5 in cycles 4-5, and v4 in 6-7, at the penalty of - Resources and resource types one clock cycle - Resource sharing and binding • (actually if we pipelined one of the - Graph models of resource binding multipliers, we wouldn't have to pay any - Conflict graphs penalty...) - Templates for architectural synthesis - A complete worked problem Later in the course, we will be examining algorithms to perform automatic binding 1/12/2006 Lecture2 17 1/12/2006 Lecture2 18 gac1 gac1

## Suggested Problems

- De Micheli, Problems 4.11, Q5 (assume all additions take one cycle) (\*\*)

- For the binding hypergraph shown in De Micheli, Fig. 4.5, construct a datapath design (you may label your registers in any way) (\*)

## Introduction: Estimation

- Part of a 4-lecture introduction

- Scheduling

- Resource binding

- Area and performance estimation

- Control unit synthesis

- This lecture covers

- Design space and the estimation problem

- Resource domination

- Estimation in general circuits

- Rent's rule

1/12/2006

Lecture3 gac1

### Design space parameters

- There can be several objectives when performing a circuit design

- small area

- low latency

- [ high throughput ] (for pipelined circuits)

- high max clock rate

- low power

- Often these objectives are conflicting, and we must trade-off between them

```

1/12/2006

```

Lecture3 gac1

2

## Design space parameters

- We can imagine a 4-dimensional space defined by (area, latency, max clock rate, power)

- Each design we could choose can be plotted as a point in this space

- Which design is "the best"?

- 1. Area = 1, Latency = 2, MCR = 2, Power = 1

- 2. Area = 2, Latency = 2, MCR = 1, Power = 1

- 3. Area = 2, Latency = 1, MCR = 1, Power = 1

- Design 1 is better than design 2

- Design 1 could be better than design 3, depending on whether it's area, latency, or MCR we're most interested in.

1/12/2006

3

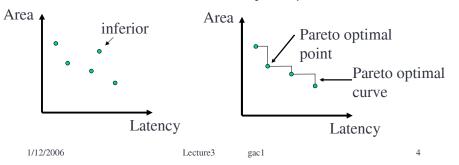

## **Design space parameters**

- Design 2 is known as an "inferior design"

it is dominated, in all objectives, by another design

- Graphically, we can imagine trading off area for latency (possibly by using more resources to reduce the number of clock cycles)

## Why estimation?

- We are not just trying to create a working circuit, but one which meets some constraints on area, power, latency, etc.

- Each time we make a high-level design decision, we want to have an estimate of the effect of this decision on these objectives.

- e.g. If I use 5 multipliers rather than 4, how will the power consumption change?

- We don't want to have to build the circuit and measure the power consumption we need a *model*

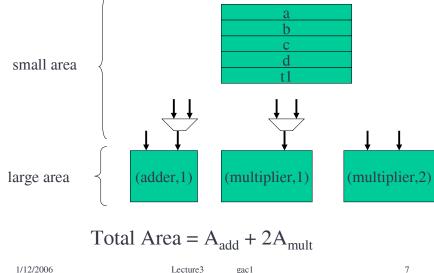

### Resource domination

- For some "resource dominated" circuits, the area, speed, power, etc. are all a function of the resources

- multiplexers, registers, etc. have an insignificant impact

- Estimation for these circuits is easy

- Area: add up the area consumed by each resource: A =  $A_{add} N_{add} + A_{mult} N_{mult} + \dots$

- Latency: known from schedule

- Often DSP circuits tend to be resource dominated

- Example: the worked example from last lecture...

| model     |               |   |           |               |   |

|-----------|---------------|---|-----------|---------------|---|

| 1/12/2006 | Lecture3 gac1 | 5 | 1/12/2006 | Lecture3 gac1 | 6 |

|           |               |   |           |               |   |

|           |               |   |           |               |   |

# Resource domination

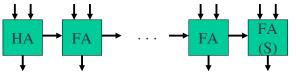

### **Example: Adder Models**

- How do we estimate the area and speed of each resource?

- Typically we have a model of how a resource is constructed, for example an n-bit ripple-carry adder:

Area =  $A_{HA} + A_{FA(S)} + (n-2)A_{FA}$  (would be determined by the set of the set of

(would be different for a CLA)

1/12/2006

## General circuits

- For non-resource dominated circuits, several other components can impact on the design objectives

- registers

- multiplexers

- wiring

1/12/2006

- control unit

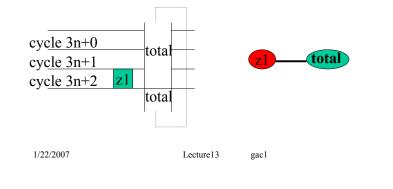

## Registers

Registers are required to store intermediate data – returning to our previous example, 3 registers are needed for temp. results (a,b,t1)

# Registers

Lecture3

gac1

- We don't always need as many registers as there are temporary variables

- If registers are expensive, we could share registers, just like we share resources

- t1 and b do not overlap in "lifetime" we could use the same register for both

- The number of temporary variables provides a good "first guess" for the number of registers we'll need in our design

## **Multiplexers**

• Multiplexers are needed to steer the right operands to the right resources

- The number and size of multiplexers required is known from the binding

- Multiplexers can consume area and add delay the delay added can depend on the number of MUX inputs

11

9

1/12/2006

## Wiring

- Even wires add area, delay, and significant power consumption to a circuit

- It has been estimated that in the next few years it will take 10 clock cycles just for a signal to cross a chip

- Unfortunately wiring is hard to estimate

- we need the binding but also the physical layout

- Rent's rule can provide a high-level model

- Relates the amount of interconnect to the number of gates in an area

- $N = KG^{\beta}$

(N = no. pins, G = no. gates)

| 1 | /12/2006 | Lecture3 | gac1 |

|---|----------|----------|------|

|   |          |          |      |

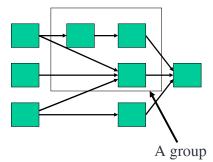

# Rent's Rule

Rent's rule gives a rough estimate how many wires will cross the boundaries of any given group.

This can be used as an estimate of wiring length

- Some examples of Rent constants

- SRAM:  $\beta$  = 0.12, K = 6

- $\mu P: \beta = 0.45, K = 0.82$

- Gate Array:  $\beta$  = 0.50, K = 1.9

```

1/12/2006

```

Lecture3 gac1

14

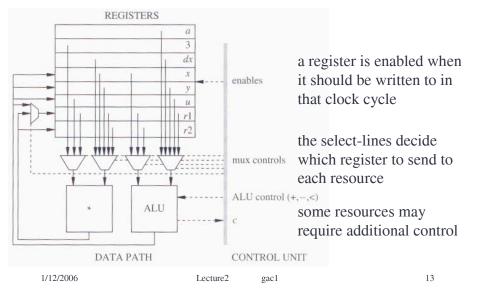

## **Control unit**

- The control unit, which provides the select lines to MUXs and enable lines to registers, itself consumes area and power

- The size of the control unit can vary significantly depending on the amount of looping and branching in the algorithm

- often DSP algorithms have very simple control

- The control unit can also impact on the max. clock rate

- We will investigate control unit synthesis in the next lecture

for now, let's simply state that the size of a controller tends to grow with

- the number of activation signals (selects, enables)

- the length of the schedule

#### 1/12/2006

15

13

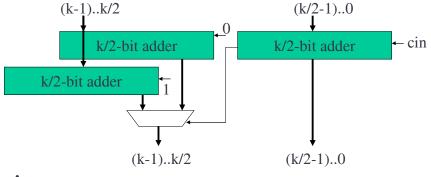

#### Worked Example 1

• A *k*-bit carry-select adder has the structure shown below

- Assume:

- each constituent adder is a ripple-carry design

1/12/2006

Lecture3

gac1

## Worked Example 1

- Derive models for the area and delay of the circuit, in terms of the wordlength *k*

- Compare the area and delay with a *k*-bit ripple carry design

- Area =  $3A_{FA}(k/2) + A_{MUX}(k/2) = c_1k$

- Delay =  $T_{FA}(k/2) + T_{MUX} = c_2k + c_3$

- Compared to a k-bit ripple carry design, the area is always larger. The delay is smaller, so long as

- T<sub>MUX</sub> < T<sub>FA</sub>(k/2) (almost certainly true for reasonable k)

```

1/12/2006

```

```

Lecture3 gac1

```

## Worked Example 2

- You are designing a circuit with gate-level Rent constants  $\beta$ =0.25, k = 1

- There are a total of 1M gates in your design. How many pins would you expect your chip to have?

- Pins  $\approx$  (1e6)^0.25  $\approx$  32

- Your chip is too big and you must split it over two chips. How many pins would you now expect?

- Let's assume an equal split. Then:

- Pins  $\approx 2(5e5)^{1}0.25 \approx 53$

- The main source of power consumption in your design is driving the external pins. Estimate the increase in power due to using two chips.

- Increase (%) = (53 32)/32 = 66% (assuming all pins equal)

```

1/12/2006

```

Lecture3 gac1

18

## Summary

- This lecture has covered

- Design space and the estimation problem

- Resource domination

- Estimation in general circuits

- Rent's rule

- Next lecture will examine the synthesis of control units

19

## Introduction: Control Synthesis

- Part of a 4-lecture introduction

- Scheduling

- Resource binding

- Area and performance estimation

- Control unit synthesis

- This lecture covers

- Microcode and microcode optimization

- Hardwired control

- Control with interacting state machines

#### 1/12/2006

Lecture4

## Why control synthesis?

- Our datapath designs have included

multiplexers, to steer data to the correct resource

- register enable signals, to select when a register should store an intermediate value

- These signals have to be generated from somewhere this is the *control unit*

Lecture4

Once we know the schedule and binding for an algorithm, we have enough information to design the controller

gac1

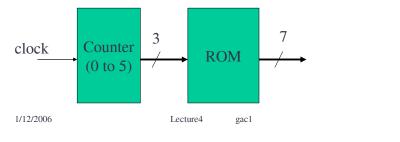

## A Control Unit

gac1

Let's take another look at the worked example from Lect 2

## A Control Unit

- The control unit for this example must:

- Cycle 1: Enable register "a", ensure the inputs of "adder1" are "i" and "j"

- Cycle 2: Ensure the inputs of "multiplier1" are 2 and "a"

- Cycle 3: Enable registers "t1" and "d"

- Cycle 4: Enable register "b", ensure the inputs of "adder1" are "t1" and "j"

- Cycle 5: Ensure the inputs of "multiplier1" are "a" and "b"

- Cycle 6: Enable register "c"

```

1/12/2006

```

1/12/2006

## Microcode vs Hardwired control

- This is the behaviour of a sequential circuit

- circuit has no inputs apart from clock for this example

- circuit has 7 binary outputs (5 enables and 2 select lines

don't need a select line for dedicated resource

"multiplier2")

- We could build this circuit as a microcode-based controller with 3 address lines ( [log<sub>2</sub> #cycles])

## Microcode vs Hardwired control

- Alternatively we could build a finite state machine (FSM) implementation specifically for this sequence

- The choice between these two implementation schemes is a *logic* synthesis problem – we will not consider it in detail

- Hardwired FSM design is itself a major topic

- could be faster, smaller, lower power than the corresponding microcode controller

- more complex to design

- less flexible (if you make the microcode ROM programmable)

- more flexible (if your design has unbounded latency nodes)

1/12/2006

Lecture4

gac1

# Horizontal Microcode

- For the example we've been working with, let's construct the ROM contents

- assume the following ordering of data outputs (MSB to LSB): a enable, t1 enable, d enable, b enable, c enable, adder1 select, multiplier1 select

- assume a 3-bit up counter, initialized to 0

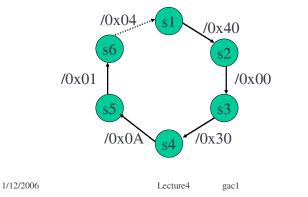

#### ROM micro-program

| Address | Data | Address | Data |

|---------|------|---------|------|

| 0x0     | 0x40 | 0x3     | 0x0A |

| 0x1     | 0x00 | 0x4     | 0x01 |

| 0x2     | 0x30 | 0x5     | 0x04 |

## Horizontal Microcode

- This is known as "horizontal" microcode

# states << # control signals (usually)</li>

- $\pi$  states  $<\pi$  control signals (usually)

- ROM has much greater width than height

We have great freedom with a borizonta

- We have great freedom with a horizontal microcode

- we design a controller for any schedule and any binding in this way

- design process is simple

- However, the ROM might be large

Lecture4 gac1

7

5

1/12/2006

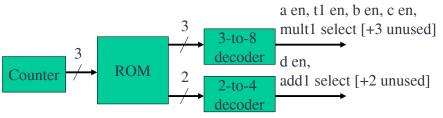

## **Microcode Optimization**

• By adding an extra (combinational) stage to our controller, we can often reduce the size of the ROM required

• The challenge is to design the ROM and decoder carefully to keep *n* small and optimize our speed, power, and area

## **Microcode Optimization**

- If we didn't require any control signals concurrently, we would only require a log<sub>2</sub>(#control sigs+1)-bit ROM data bus

- we could then use an *n* to 2<sup>n</sup> decoder to generate the control signals

- (revision... an *n* to 2<sup>n</sup> decoder asserts one of 2<sup>n</sup> different possible outputs depending on the *n*-bit binary encoding of the input. For example a 2-to-4 decoder has truth table 00->0001, 01->0010, 10->0100, 11->1000)

- Why (+1)?

- because we may not want to assert *any* control signals in some clock cycles

| 1/12/2006 | Lecture4 | gac1 | 9 | 1/12/2006 | Lecture4 | gac 1 | 10 |

|-----------|----------|------|---|-----------|----------|-------|----|

|           |          |      |   |           |          |       |    |

# **Microcode Optimization**

- But if we don't allow concurrent control signals then we don't allow parallelism!

- the advantage of a hardware implementation is destroyed

- Solution:

- Partition the set of control signals into subsets which are not required concurrently

- For our example, one possible partition is:

- {a enable, t1 enable, b enable, c enable, multiplier1 select}, {d enable, adder1 select}

- We can encode each of these partitions separately

#### 1/12/2006

Lecture4 gac1

11

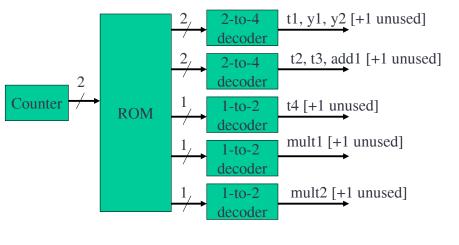

## **Microcode Optimization**

- We need  $\lceil \log_2 6 \rceil = 3$  bits to encode the first subset, and  $\lceil \log_2 3 \rceil = 2$  bits to encode the second subset

- Our controller now looks like this

• We have saved two bits of ROM data bus!

```

1/12/2006

```

## **Microcode Optimization**

- Assume we order the ROM databus (MSB to LSB): first subset encoding, second subset encoding

- Assume we order the outputs of each decoder in the order shown on the figure in the prev. slide

- A suitable ROM program is now:

| Address | Data    | Address | Data    |

|---------|---------|---------|---------|

| 0x0     | 0b11100 | 0x3     | 0b10110 |

| 0x1     | 0b00000 | 0x4     | 0b01100 |

| 0x2     | 0b11011 | 0x5     | 0b10000 |

1/12/2006

Lecture4 gac1

13

15

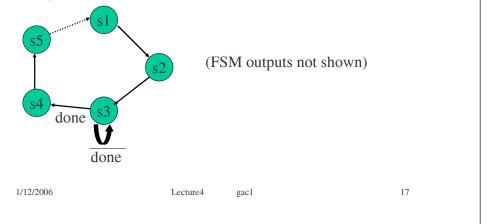

## Hardwired FSM synthesis

- Alternatively, we could view controller design as a standard FSM synthesis problem

- One state per clock cycle

1/12/2006

1/12/2006

- Most importantly, it is easy to specify FSM behaviour for sequencing graphs with nodes of unbounded latency

- The same optimization technique applied to microcode can also be applied to the FSM design

gac1

14

16

Lecture4

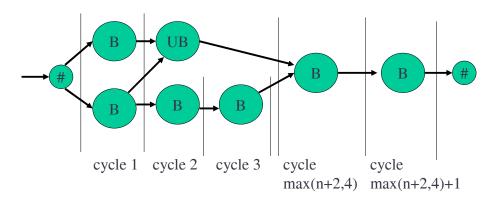

## **Bounded Latency Example**

• Considering our previous example as an FSM leads to the following state transition graph, which can easily be coded in your favourite hardware description language

## **Unbounded Latency Operations**

• Let's consider the unbounded latency example from Lecture 1

Lecture4

gac1

## **Unbounded Latency Example**

- It is easy to create an FSM for this example

- we must wait for "done" signal from unbounded latency resource => we have inputs to the controller as well as outputs

## Local Controllers

- So far we have assumed that there is one large controller for the whole circuit

- this can be efficient as it allows the overhead of controller design and implementation to be shared by many control signals

- however it may be impractical for large circuits due to the need to route control signals across the chip

gac1

18

- Each control signal (or set of control signals) could have its own controller

- Such a control unit is called "distributed control". Using one large controller is called "centralized control" or "lumped control"

Lecture4

1/12/2006

| W  | or | ked | Exa | mpl | e |

|----|----|-----|-----|-----|---|

| vv |    | NGU |     | ΠΡΙ | C |

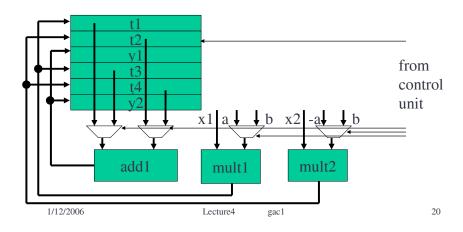

- You are designing a hardware implementation of a discrete cosine transform (DCT) algorithm. The inner loop of your algorithm is shown overleaf, along with a schedule and binding. (x1, x2 are inputs; y1, y2 are outputs). Both multipliers and adders take one clock cycle.

- (a) draw a datapath for this circuit

- (b) design a horizontal microcode-based controller for this circuit

- (c) by making your design "non-horizontal", minimize the size of ROM required

- (d) re-design your controller so that each functional unit has its own controller, which controls the select-lines for its input multiplexers, and the enable lines for its output registers

#### 1/12/2006

19

### Worked Example (a)

| t1 = a*x1;    | // Cycle 1, mult1       | t3 = b*x1;    | // Cycle 2, mult1 |

|---------------|-------------------------|---------------|-------------------|

| t2 = b*x2;    | // Cycle 1, mult2       | t4 = -a*x2;   | // Cycle 2, mult2 |

| y1 = t1 + t2; | // <b>Cycle 2, add1</b> | y2 = t3 + t4; | // Cycle 3, add1  |

## Worked Example (b)

- 3 cycles =>  $\lceil \log_2 3 \rceil$  = 2 bit ROM address

- 6 registers + 3 mux select lines = 9 control signals

- assume data bus ordering (MSB to LSB): enables (t1,t2,y1,t3,t4,y2); select lines (add1, mult1, mult2)

| Address   | Data        | Address | Data        |

|-----------|-------------|---------|-------------|

| 0x0       | 0b110000000 | 0x2     | 0b000001100 |

| 0x1       | 0b001110011 |         |             |

| 1/12/2006 | Lecture4    | gac1    | 21          |

## Worked Example (c)

- In general, finding the subsets that minimize the size of ROM is a "hard" problem (more on the meaning of "hard" in a future lecture...)

- We will therefore find a "good", but not necessarily optimum set of subsets

- Set 1: {t1, y1, y2} => need 2 bits

- Set 2: {t2, t3, add1} => need 2 bits

- Set 3: {t4} => need 1 bit

- Set 4: {mult1} => need 1 bit

- Set 5: {mult2} = need 1 bit

```

1/12/2006

```

Lecture4 gac1 22

## Worked Example (c)

gac1

## Worked Example (c)

- Applying the techniques described in the lecture results in the table below (for the order in the figure on the prev. slide) This results in compression from 9 to 7 data bits.

- Clearly this could be further compressed, as from below bit6=bit4, bit5=bit3, bit2=bit1=bit0. Together this results in compression from 9 to 3 data bits.

| Address   | Data      | Address | Data      |

|-----------|-----------|---------|-----------|

| 0x0       | 0b1111000 | 0x2     | 0b0101000 |

| 0x1       | 0b1010111 |         |           |

| 1/12/2006 | Lecture4  | gac1    | 24        |

Lecture4

1/12/2006

## Worked Example (d)

- For a horizontal implementation, simply pick the relevant output bits from the lumped-controller implementation

- Assume orderings (MSB to LSB):

- add1 controller: add1, y1, y2

- mult1 controller: mult1, t1, t3

- mult2 controller: mult2, t2, t4

| Address   | add1 Data | mult1 Data | mult2 Data |

|-----------|-----------|------------|------------|

| 0x0       | 0b000     | 0b010      | 0b010      |

| 0x1       | 0b010     | 0b101      | 0b101      |

| 0x2       | 0b101     | 0b000      | 0b000      |

| 1/12/2006 | Lecture4  | gac1       | 25         |

## Summary

- This lecture has covered

- Microcode and microcode optimization

- Hardwired control

1/12/2006

- Control with interacting state machines

- A detailed worked example

- During the next lecture we will start to look at some of the mathematical framework which helps us do architectural synthesis

gac1

Lecture4

26

## Suggested Problems

- Some multiplication algorithms have datadependent delay. Assume we want to use one such multiplier, and one adder (with delay 1 cycle) to implement the differential equation inner-loop introduced in Lecture 1.

- (a) perform a scheduling, treating the multipliers as elements of unknown latency

- (b) sketch the datapath of the resulting design

- (c) draw a FSM state-transition diagram for your design

1/12/2006

#### Graphs **Graphs & Combinatorial Problems** Formal Definition: A new part of the course – will cover the more - A graph G is a finite nonempty set V together with an theoretical aspects required in later lectures [irreflexive], symmetric relation E on V- Graphs, cliques, and colouring • The relation *E* relates vertices to other vertices and is known - Algorithms and intractability as the edge relation, or "edge set" Linear programming and integer linear programming • If relation *E* is symmetric, it means that - Shortest and longest path algorithms • $(a,b) \in E \implies (b,a) \in E$ an edge has no concept of "direction" This lecture covers • · In mathematics, an edge relation is usually considered - Definition of graph (revision), clique, and clique number irreflexive: - Graph colouring, chromatic number • ¬∃a : (a.a)∈E - Interval graphs - engineers often relax this constraint (hence the brackets) 1/15/2007 1/15/2007 2 Lecture5 Lecture5 gac1 gac1

## **Directed Graphs**

- Formal definition:

- A directed graph G is a finite nonempty set V together with an [irreflexive] relation E on V

- This time the concept of direction is implicit, as we could have (a,b)∈E and (b,a)∉E

- You may see directed graphs referred to as "digraphs"

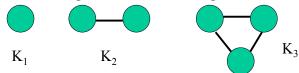

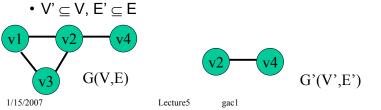

#### Cliques

• A *complete graph* is a special type of graph where all possible edges are in the edge set

A subgraph G'(V',E') of a graph G(V,E) is a graph whose vertex and edge sets obey

3

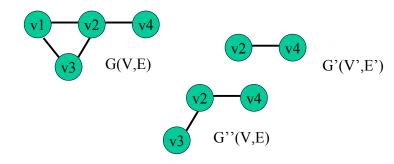

### Cliques

• A *clique* is a complete subgraph

• G' is a clique. G'' is not a clique (but it is a subgraph of G)

Lecture5

## **Clique Number**

• The *clique number*  $\omega(G)$  of a graph G is the size of the node set of its largest clique

- This graph has cliques with the following node subsets:

- $\{v1\}, \{v2\}, \{v3\}, \{v4\}, \{v1, v2\}, \{v1, v3\}, \{v2, v3\}, \{v2, v4\},$  $\{v1, v2, v3\}$

- Its clique number is 3

Lecture5 gac 1 6

## Graph Colouring

gac1

· Graph colouring is the process of labelling each node of a graph such that no two connected nodes share the same label

- The graph above is coloured with three different colours

- Graph colouring can model many problems

- e.g. colouring a conflict graph (Lecture 2) will result in a resource binding gac1

1/15/2007

1/15/2007

7

5

## A Colouring Algorithm

A simple algorithm for colouring a graph is given below

```

Colour_Graph( G(V,E) )

begin

foreach v \in V

c = 1:

while \exists (v, v') \in E: v' has colour c

c = c + 1:

label v with colour c }

end

```

• This will always correctly colour a graph, but the number of distinct colours used depends on the order in which the nodes are visited

```

1/15/2007

```

## **Chromatic Number**

- The smallest number of colours with which it is possible to colour a graph G is called its chromatic number χ(G)

- For a general graph, finding  $\chi(G)$  is a "hard" problem

- the algorithm presented does not guarantee a colouring with  $\chi(\textbf{G})$  colours

- we'll be discussing "hard" problems next lecture

- In resource binding, the chromatic number tells us the minimum number of distinct resources required

- Since every node in a clique must be coloured differently to every other node in a clique,

9

11

•  $\omega(G) \leq \chi(G)$

| 1/15/2007 | Lecture5 | gac1 |

|-----------|----------|------|

|           |          |      |

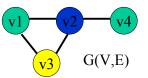

## **Interval Graphs**

- Luckily, not all graphs are "hard" to colour. One type of graph which is easy to colour with the minimum number of colours is an "interval graph"

- An *interval graph* is a graph whose vertices can be put in one-to-one correspondence with a set of intervals, such that two vertices are connected by an edge iff the corresponding intervals intersect

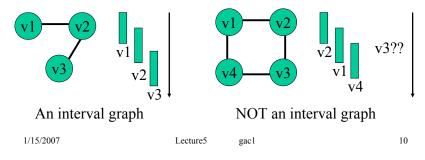

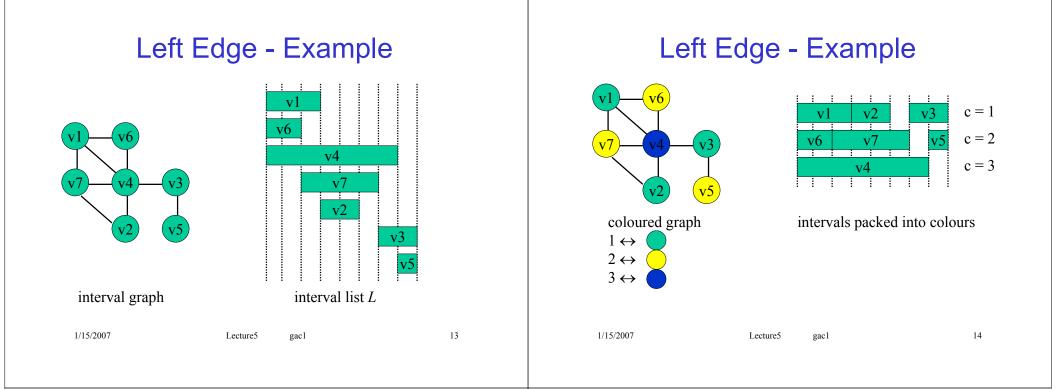

## The Left Edge Algorithm

- The left-edge algorithm colours interval graphs optimally.

- Let us denote by *I<sub>i</sub>* and *r<sub>i</sub>* the left-most and right-most point of the interval corresponding to vertex *v<sub>i</sub>*.

#### Left\_Edge( G(V,E) )

```

begin

sort nodes in ascending order of left edge – store in L

c := 1;

while( not all vertices have been coloured ) {

r := 0;

while( \exists an element s in L with I_s > r) {

v_s := first node in L with I_s > r;

r:= r_{s};

label v_s with colour c

L := L \setminus \{v_s\}; }

c := c + 1; }

end

I/15/2007 LectureS gacl

```

# The Left Edge Algorithm

- Some set theory:

- \ represents set subtraction

- $X \setminus Y = \{ z : z \in X \land z \notin Y \}$

- The left edge algorithm tries to colour as many intervals as possible with one colour, before moving on the the next colour

- Left Edge was originally introduced to pack wire segments tightly on a VLSI layout. It is now used for many other purposes – particularly resource binding.

```

1/15/2007

```

## Summary

- This lecture has covered

- graphs and digraphs

- cliques and clique number

- colouring and chromatic number

- interval graphs and the Left Edge algorithm

- Next lecture will examine the ideas behind designing "good" algorithms, and what it means for a problem to be "hard"

## **Suggested Problems**

- For the graph below, apply the general colouring algorithm for the following two vertex orders. Compare and contrast your results. (\*)

- (a) (v1, v2, v3, v4)

- (b) (v1, v4, v3, v2)

1/15/2007

By applying the left-edge algorithm, or otherwise, demonstrate that one of the two orders above results in an optimum colouring (\*)

15

## Algorithms and Intractability

- Part of our 4-lecture "theory break"

- Graphs, cliques, and colouring

- Algorithms and intractability

- Linear programming and integer linear programming

- Shortest and longest path algorithms

- This lecture covers

- The definition of an "algorithm"

- Polynomial-time and intractability

- P and NP

- Polynomial reduction, NP-completeness and NPhardness

Lecture6

gac1

## The Purpose of This Lecture

- Synthesis is all about writing algorithms to solve problems in digital design

- This lecture will consider some of the more theoretical aspects concerning

- problems, algorithms, and complexity

- We will formalize what is meant by a "hard" problem

- You will **not** be required to prove the hardness of any unseen problems as part of this course

- You may be required to describe the ideas of hardness

| 1/15/2007 | 7 |

|-----------|---|

|-----------|---|

Lecture6 gac1

2

## Problems and Instances

- We have already discussed several problems and algorithms. We will now take a few minutes to formalize these concepts

- A *problem* is a general question to be answered, usually possessing several parameters, whose values are left unspecified

- e.g. Can I schedule a DFG G(V,E) to complete within  $\lambda$  cycles using at most *n* multipliers?

- An *instance* of a problem is obtained by specifying particular values for all parameters

- e.g. Can I schedule the DFG given in Lecture 1, slide 5, to complete within 10 cycles using at most 2 multipliers?

#### 1/15/2007

3

#### "Hard" Problems

"I can't find an efficient algorithm, I guess I'm just too dumb."

[Garey & Johnson 1979]

#### "Hard" Problems

"I can't find an efficient algorithm, because no such algorithm is possible!"

[Garey & Johnson 1979]

5

1/15/2007

Lecture6 gac1

#### "Hard" Problems

## Algorithms and Efficiency

- An *algorithm* is a general step-by-step procedure for solving problems

- An algorithm is said to solve a problem Π if the algorithm can be applied to any instance of Π and is guaranteed to always produce a solution for that instance

- An *efficient* algorithm is one that solves the problem "quickly"

- there are other factors such as memory usage, but we will ignore these

## Complexity

- Usually, we can describe the worst-case performance of an algorithm as a function of the "size" *n* of the problem instance

- We generally are concerned with the "big picture" of how performance scales with size (especially for large sizes), rather than specific execution times

- The Big-Oh notation allows us to express this behaviour

- $O(n), O(n^2), O(e^n)$

- An algorithm is O( f(n) ) if its worst case performance is bounded by *k* f(*n*) for large *n*

7

1/15/2007

## Complexity

- Example: A (good) algorithm to add n numbers will be O(n)

- Example: An algorithm to sort *n* numbers in order. You may be familiar with

- quicksort:  $O(n^2)$

- heapsort: O(n log n)

- Example: An algorithm which considers all possible *k*-colourings that a graph could have would be O(*k<sup>n</sup>*)

## Polynomial vs Exponential Time

- A polynomial-time algorithm is one which has O( p(n) ) for some polynomial p(·).

- An exponential-time algorithm is any algorithm which is not polynomial-time.

- Clearly for large *n*, exponential-time algorithms take much longer than polynomial-time algorithms

- the main distinction is thus: "is this algorithm exponential (bad) or polynomial (good)?"

- the order of the polynomial is of secondary concern

- All problems which can be solved by polynomial algorithms are said to belong to the class *P*

| 1/15/2007 | Lecture6 gac1 | 9 | 1/15/2007 | Lecture6 gac1 | 10 |

|-----------|---------------|---|-----------|---------------|----|

|           |               |   |           |               |    |

## Nondeterministic Polynomial Time

- To complicate matters, computer scientists have come up with another class, *NP* (nondeterministic polynomial).

- A problem is in *NP* if a *solution* to the problem can be *checked* in polynomial time

- this doesn't mean it has to be solvable in polynomial time

- Example:

- scheduling G(V,E) in time  $\lambda$  given resource constraints may or may not be solvable in polynomial time

- it is clear that given a schedule, we could check in polynomial time that it is a valid schedule and it completes within  $\lambda$  cycles

## Want to Earn Some Money?

- The problem "does *P* = *NP*?" is unsolved

- If you solve it you will

- be famous

- win \$2,000,000 from www.claymath.org

- ...but don't let it distract you from your degree!

## **Polynomial Reduction**

- Many interesting and difficult problems (like scheduling) are in NP but we don't know whether they're in P

- Since it is generally hard to prove that a given problem is not in *P*, we instead concentrate on proving that its "at least as hard" as a known hard problem

- If we can transform any instance of a hard problem  $\Pi^{\text{H}}$  into an instance of our problem  $\Pi$ , and that transformation can be done in polynomial time, then

- if we can solve  $\Pi$ , we can solve  $\Pi^{H} \Rightarrow \Pi$  is also hard!

1/15/2007

Lecture6 gac1

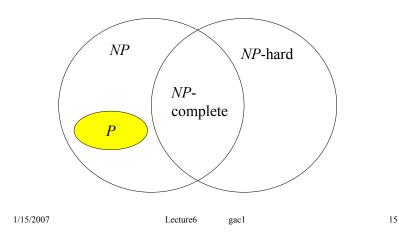

### NP-completeness & NP-hardness

- There are some problems which are in *NP* and which are known to be at least as hard as any other problem in *NP*.

- these are called NP-complete

- NP-complete problems are of particular interest, as if a solution to any NP-complete problem can be found in polynomial time then P = NP

- A problem which is at least as hard as an *NP*-complete problem is called *NP*-hard

- this is our formal definition: for "hard problem" read "NPhard problem"

```

1/15/2007

```

13

Lecture6 gac1

14

## A Hierarchy of Problems

Assuming P ≠ NP, this is how our "world of problems" looks

### **Proving Hardness**

- Proving NP-hardness requires two stages

- pick a known NP-hard problem

- demonstrate a transformation from this problem to your problem

- There are some *NP*-complete problems which form the basis of many proofs. We will look at one: Partition

- Partition: Given a finite set A and a measure s(a) ∈ Z<sup>+</sup> for each a ∈ A, is there a subset A' ⊆ A such that the following equation holds?

$$\sum_{a\in A'} s(a) = \sum_{a\in A-A'} s(a)$$

gac 1

| <ul> <li>Proving Hardness</li> <li>An example instance of "partition": <ul> <li>A = {v1, v2, v3} with s(v1) = 1, s(v2) = 2, s(v3) = 1</li> </ul> </li> <li>for this instance, the answer is clearly "yes": <ul> <li>A' = {v2} or A' = {v1, v3}</li> </ul> </li> </ul> | <ul> <li>Example: Scheduling is NP-hard</li> <li>To finish off, we'll prove the NP-hardness of an example problem (a simple form of scheduling)</li> <li>Our simple scheduling problem has no data dependencies and only one type of operation</li> <li>Remember that you won't be asked to do such a proof for an unseen problem, but this proof has been included <ul> <li>for completeness</li> <li>to give a more "practical" end to a highly theoretical lecture</li> <li>to justify past and future comments about scheduling being a "hard" task to perform</li> </ul> </li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/15/2007 Lecture6 gac1 17                                                                                                                                                                                                                                            | 1/15/2007 Lecture6 gac1 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Scheduling is NP-hard

- Let's start by defining our problem:

- given a finite set A of operations, a latency

d(a) ∈ Z<sup>+</sup> for each a ∈ A, a number m ∈ Z<sup>+</sup> of resources, and a deadline λ ∈ Z<sup>+</sup>

- is there a schedule such that all operations complete within the deadline and no more than *m* resources are used?

## Scheduling is NP-hard

- Let us rephrase the question:

- is there a partition  $A = A_1 \cup A_2 \cup \ldots \cup A_m$  of A into *m* disjoint subsets such that

$$\max_{1\leq i\leq m}\left\{\sum_{a\in A_i}d(a)\right\}\leq\lambda$$

*A<sub>i</sub>* represents the set of operations assigned to processor *i*, and no two operations can be executed at the same time on a single resource

19

1/15/2007

## Scheduling is NP-hard

• Let's consider a special case of our problem, for m=2 and  $\lambda = \frac{1}{2} \sum d(a)$

$$\lambda = -\frac{1}{2} \sum_{a \in A} a(a)$$

- Then the problem reduces to:

- given a finite set A, and a value  $d(a) \in Z^+$  for each  $a \in A$

- is there a partition into 2 disjoint subsets A' and A A' such that

$$\max\left\{\sum_{a\in A'} d(a), \sum_{a\in A-A'} d(a)\right\} \leq \frac{1}{2} \sum_{a\in A} d(a)$$

## Scheduling is NP-hard

• Rewriting, we require

$$\frac{1}{2}\max\left\{\sum_{a\in A'}d(a)-\sum_{a\in A-A'}d(a),\sum_{a\in A-A'}d(a)-\sum_{a\in A'}d(a)\right\}\leq 0$$

• But for any k,  $max(k,-k) \le 0 \Rightarrow k = 0$ , so we require

$$\sum_{a\in A'} d(a) = \sum_{a\in A-A'} d(a)$$

• But this is the "partition" problem. So "partition" is a special case of our problem and hence our problem is NP-hard

| 1/15/2007 | Lecture6 | gacl | 21 | 1/15/2007 | Lecture6 | gacl | 22 |

|-----------|----------|------|----|-----------|----------|------|----|

|           |          |      |    |           |          |      |    |

## Summary

- · This lecture has covered

- The definition of an "algorithm"

- Polynomial-time and intractability

- P and NP

- Polynomial reduction, NP-completeness and NPhardness

- Next lecture we will look at the (NP-hard!) problem of Integer Linear Programming (ILP) and how we can use ILP solving software to help us optimize our hardware

1/15/2007

## [Integer] Linear Programming

- Part of our 4-lecture "theory break"

- Graphs, cliques, and colouring

- Algorithms and intractability

- Linear programming and integer linear programming

- Shortest and longest path algorithms

- This lecture covers

- Mathematical programming, integer / mixed-integer programming, and linear programming

Lecture7

Slack variables

1/15/2007

- Application example: Capital budgeting

| Mathematical | Program | ming |

|--------------|---------|------|

|              |         |      |

• Mathematical "programming" is the name given to the branch of mathematics that considers the following optimization problem:

$\max f(x), \quad x \in S \subseteq R^n$

- Here *R<sup>n</sup>* represents the set of *n*-dimensional vectors of real numbers, and *f* is a real-valued function defined on *S*. *S* is the *constraint set* and f is the *objective function*.

- By choosing f and S appropriately, we can model a wide variety of real-life problems in this way.

gac 1

Lecture7

| Feasibility | and | Optim | ality |

|-------------|-----|-------|-------|

gac1

- Any  $x \in S$  is called a *feasible solution*

- If the there is an  $x^o \in S$  such that

$f(x) \leq f(x^{o})$  for all  $x \in S$

then x° is called an optimal solution

The aim is to find an optimal solution for a given f and S

## **Integer Programming**

• An integer programming problem is one where *S* is restricted to have only integer values

$$S \subseteq Z^n \subseteq R^n$$

- A mixed integer programming problem is one where some elements of *S* are restricted to integers

- Integer programming problems are typically harder than the equivalent real problem. You can gain an intuition why by considering the following problems

- find the value of x minimizing  $\cos(x/5)$

• 5π

1/15/2007

- find the integer value of x minimizing  $\cos(x/5)$

• round( 5π ) ? round ( 5π + 10π ) ? ...

Lecture7 gac1

2

1/15/2007

gac1

3

#### Linear Programming

• Problems where *f* and *S* are restricted to linear form are of particular interest

$f(x) = c^{T}x,$   $S = \{ x \mid Ax = b, x \ge 0 \}$

- c is an n x 1 vector, A is an m x n matrix and b is an m x 1 vector

- Imposing the linearity constraints restricts the domain of problems, but allows us to use known solution techniques

- For general x, these problems can be solved exactly (e.g. Simplex technique). For integer x, the problem is *NP*-complete.

```

1/15/2007

```

```

Lecture7 gac1

```

#### Why Are We Interested?

- We are interested in expressing problems as integer or mixed integer linear programs because

- it provides a way to formalize the problem

- we can apply known general techniques to solve the problem

- lots of software exists to solve MILPs (e.g. lp\_solve, available free from the web)

- I will be introducing ILP formulations for scheduling and resource binding in later lectures

```

1/15/2007

```

Lecture7 gac1

6

## Modelling Complex Problems

- At first glance, linear constraints may seem very restrictive this is not necessarily the case, if you build your model carefully.

- Here are three types of constraint that could be useful in synthesis

- inequalities (e.g.  $x1 + x2 \le b1$ , rather than x1 + x2 = b1)

- dichotomy (e.g. x1 + x2  $\leq$  b1 OR x3 + x4  $\leq$  b2)

- conditionals (e.g. x1 + x2  $\leq$  b1  $\Rightarrow$  x3 + x4  $\leq$  b2)

- We will only be considering the first in this brief introduction. If you wish to use the others,

- R.S. Garfinkel and G.L. Nemhauser, "Integer Programming", Wiley and Sons, 1972

1/15/2007

7

5

#### Inequality

- Inequality constraints can easily be introduced by adding an extra variable

- For example, consider the program:

max  $2x_1 + 3x_2$  subject to  $x_1 + x_2 \le 10$

This is the same as

max  $2x_1 + 3x_2$  subject to  $x_1 + x_2 + x_3 = 10$

- For " $\geq$ ", we would insert (- $x_3$ ) into the constraint

- The extra variable is called a slack variable it does not appear in the objective function

- Because this is so straight-forward, many ILP solving programs allow you to express constraints with inequality directly. From now on, we will use inequalities freely without considering slack variables explicitly

#### **Example: Capital Budgeting**

- From Garfinkel and Nemhauser (1972):

- A firm has *n* projects that it would like to undertake, but due to budget limitations, not all can be selected. In particular, project *j* has a value of  $c_j$ , and requires an investment of  $a_{ij}$  in the time period *i*, *i* =1,...,*m*. The capital available in time period *i* is  $b_j$ .

- Problem: Maximize the total value, subject to budget constraints

gac1

Lecture7

#### **Example: Capital Budgeting**

- Let's introduce a set of variables *x<sub>j</sub>*, which we interpret as:

- $-x_j = 1 \Rightarrow \text{project } j \text{ is selected}$

- $-x_j = 0 \Rightarrow$  project *j* is not selected

- Then the objective function can be formulated as

$$\sum_{j=1}^{n} c_{j} x_{j}$$

· The constraints are

$$\sum_{j=1}^{n} a_{ij} x_j \le b_i, i = 1, ..., m; \quad x_j \le 1, j = 1, ..., n$$

```

1/15/2007

```

Lecture7 gac1

10

### Summary

- This lecture has covered

- Mathematical programming, integer / mixedinteger programming, and linear programming

- Slack variables

- Application example: Capital budgeting

- Next lecture (the last in our "theory break"), looks at finding the shortest and longest path through a graph

1/15/2007

11

#### Path Problems and Algorithms

- Part of our 4-lecture "theory break"

- Graphs, cliques, and colouring

- Algorithms and intractability

- Linear programming and integer linear programming

- Shortest and longest path algorithms

- This lecture covers

- Edge-weighted graphs, shortest and longest path problems

- Longest path through a DAG

- Longest path through a general graph: Liao-Wong

- Longest path as a LP

```

1/15/2007

```

Lecture8

gac1

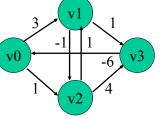

#### Edge Weighted Graphs

- An edge-weighted graph is a graph *G*(*V*,*E*) together with a weighting function *w*: *E* → R

- We can represent this graphically by annotating each edge e ∈ E with its weight w(e)

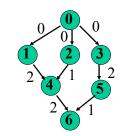

An edge weighted DAG

An edge-weighted graph with cycles Lecture<sup>8</sup> gacl 2

#### Shortest and Longest Path

• A *path* through a graph is an alternating sequence of vertices and edges

A path between vertices v0 and v3, with total edge weight 3+1 = 4 has been highlighted

#### Shortest and Longest Path

- The *longest path* problem is to find a path of maximum total weight between a given "source" vertex and any other vertex in the graph

- the shortest path problem is defined similarly

- we will consider only longest path problems shortest path can then be achieved by inverting all weights w'(e) = -w(e)

- Bellman's equations define the total weight of any vertex v

$$s_v = \max_{(u,v)\in E} (s_u + w(u,v))$$

gacl

1/15/2007

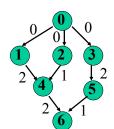

#### Longest Path Through a DAG

- The longest path through a DAG is an easier problem than the equivalent for a general graph

- This is because we can find an order of nodes to visit such that the right-hand side of each Bellman's equation is known

- For our example DAG, let's choose vertex 0 as our source. Then  $s_0 = 0$ . If we now proceed to apply Bellman's equations in the order ( $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_4$ ,  $s_5$ ,  $s_6$ ), we can determine the total weight for each node

$- s_1 = 0, s_2 = 0, s_3 = 0, s_4 = 2, s_5 = 2, s_6 = 4$

- Note that this would not work with an arbitrary order. We must calculate s<sub>v</sub> before s<sub>u</sub> for all (v,u) ∈ E

- For a graph with cycles, it is not possible to find such an order

| 1/15/2007 | Lecture8 | gac1 |

|-----------|----------|------|

|           |          |      |

|           |          |      |

#### DAG Algorithm

Below is one possible algorithm (apologies to the recursionphobics)

> Algorithm DAG\_Longest\_Path( G(*V*,*E*), source ) Set  $s_{source} = 0$ ; foreach  $v \in V$ Find\_DAG\_Path( G(*V*,*E*), v); end DAG\_Longest\_Path

Algorithm Find\_DAG\_Path( G(*V,E*), *v* ) if already know *s<sub>v</sub>* return; else

foreach  $(u,v) \in E$ Find\_DAG\_Path( G(*V*,*E*), *u* ) Apply Bellman's equation to find  $s_v$ end Find\_DAG\_Path

```

1/15/2007

```

5

7

Lecture8 gac1

#### DAG example

- Let's assume the vertices are stored in V in an arbitrary order – say (4,1,2,3,5,0,6)

- A call to DAG\_Longest\_Path( G(V,E), 0 ) will set s<sub>0</sub> = 0, and then follow the following execution profile

- 1. Find\_DAG\_Path( G(V,E), 4 )

- 1. Find\_DAG\_Path( G(V,E), 1 )

- 1. Find\_DAG\_Path( G(V,E), 0 )

- 2. Calculate  $s_1 = 0$

- 2. Find\_DAG\_Path( G(V,E), 2 )

- 1. Find\_DAG\_Path( G(V,E), 0 )

- **2.** Calculate  $s_2 = 0$

```

3. Calculate s_4 = 2

```

1/15/2007

#### **DAG Example**

- 2. Find\_DAG\_Path( G(V,E), 1 )

- 3. Find\_DAG\_Path( G(V,E), 2 )

- 4. Find\_DAG\_Path( G(V,E), 3 )

- 1. Find\_DAG\_Path( G(V,E), 0 )

- 2. Calculate  $s_3 = 0$

- 5. Find\_DAG\_Path( G(V,E), 5 )

- 1. Find\_DAG\_Path( G(V,E), 3 )

- 2. Calculate  $s_5 = 2$

- 6. Find\_DAG\_Path( G(V,E), 0 )

- 7. Find\_DAG\_Path( G(V,E), 6 )

- 1. Find\_DAG\_Path( G(V,E), 4 )

- 2. Find\_DAG\_Path( G(V,E), 5 )

- 3. Calculate  $s_6 = 4$

#### **General Longest Path**

- Many algorithms to find the longest path of general graphs have been proposed in the literature

- We will consider Liao and Wong's algorithm as it is very efficient for cases where the graph edge set *E* ∪ *F* can be partitioned into a "forward" edge set *E* and a feedback edge set *F* where *G*(*V*,*E*) is a DAG and |*E*| >> |*F*|

- this is often the case with graphs arising in synthesis we will consider some of these in future lectures

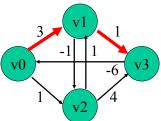

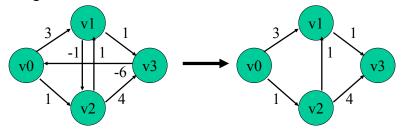

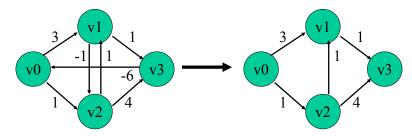

#### **Example Edge Set Partition**

• Consider our example graph. If we remove the edges labelled "-1" and "-6", we obtain a DAG

• The remaining edges form the set *E*, whereas the two we removed form the set *F*

| 1/15/2007 | Lecture8 gac1 | 9 | 1/15/2007 | Lecture8 gac1 | 10 |

|-----------|---------------|---|-----------|---------------|----|

|           |               |   |           |               |    |

#### **General Algorithm**

```

Algorithm Liao_Wong( G(V, E \cup F), source )

for j = 1 to | F | + 1 {

DAG_Longest_Path( G(V, E), source);

flag = TRUE;

foreach (u, v) in F {

if s_v < s_u + w(u, v) {

flag = FALSE;

E = E \cup \{ (source, v) \};

w(source, v) = s_u + w(u, v);

}

if(flag) return;

}

end Liao Wong

```

#### **Algorithm Description**

- Liao Wong first applies the DAG algorithm on the forward edges only. If no feedback edge provides a longer path alternative, the algorithm terminates

- If a longer path alternative is found, the algorithm models this as an extra forward edge directly from the source

- This process is repeated, until no more changes to the edge set are necessary

- It is provable that if the graph contains no cycles where the sum of weights around the cycle is positive, the outer loop need only be executed at most |*F*|+1 times.

11

1/15/2007

#### **General Example**

• Let us examine our example graph

Performing our initial DAG longest path, with v0 as the source, leads to

$- s_{v0} = 0, s_{v1} = 3, s_{v2} = 1, s_{v3} = 5$

| 1/15/2007 | Lecture8 | gacl | 13 |

|-----------|----------|------|----|

|           |          |      |    |

## **General Example**

- We now examine each of the feedback edges in turn

- for edge (v3,v0),  $s_{v0} \geq s_{v3} 6 \ \ (0 \geq -1),$  so no change needs to be made

- for edge (v1,v2),  $s_{v2} < s_{v1} 1$  (1 < 2), so we must insert a new forward edge (v0,v2) with weight 2 [in this example, (v0,v2) is already in E, so we just modify the weight]

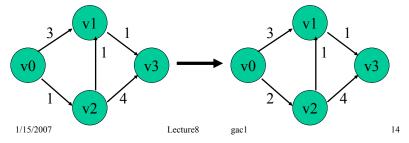

#### **General Example**

Calculating the longest path on the modified DAG leads to

$- s_{v0} = 0, s_{v1} = 3, s_{v2} = 2, s_{v3} = 6$

- Examining each feedback edge in turn

- for edge (v3,v0),  $s_{v0} \geq s_{v3} 6 \ (0 \geq 0),$  so no change needs to be made

- for edge (v1,v2),  $s_{v2} \geq s_{v1} 1$  (2  $\geq$  2), so no change needs to be made

- At this point, the algorithm terminates as no changes are necessary

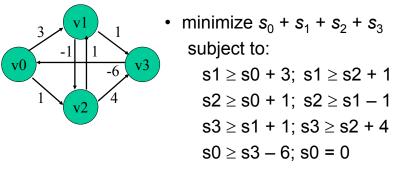

#### Longest Path as a LP

- To keep up our interest in LP, let's formulate the longest path problem as a LP

- Let's revisit Bellman's equations:

$$s_{v} = \max_{(u,v)\in E}(s_{u} + w(u,v))$$

• A necessary condition for satisfaction is:

$\forall (u,v) \in E, \quad s_v \geq s_u + w(u,v) \quad (*)$

• The minimum values of  $s_v$  that satisfy (\*) are the solutions to Bellman's equations

15

1/15/2007

#### Longest Path as a LP

- We can write this as: minimize  $\sum_{v \in V} s_v$  subject to:  $s_v \ge s_u + w(u, v)$  for all  $(u, v) \in E$ and  $s_{source} = 0$

- This is a standard LP formulation (c.f. lecture 7), which can easily be cast in matrix notation Ax ≥ b if required

#### LP Example

• For our general graph example, the LP objective function and constraints are given below

| 1/15/2007 | Lecture8 gac1 | 17 | 1/15/2007 | Lecture8 gac1 |  |

|-----------|---------------|----|-----------|---------------|--|

|           |               |    |           |               |  |

|           |               |    |           |               |  |

#### Some Applications

- Longest and shortest path problems have many real-life applications, including

- Circuits: Determining the critical path in a circuit, and hence the performance of that circuit

- Transport: Finding the (shortest/cheapest/least fuel) route between two places

- Networking and Comms: Shortest path through a network

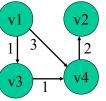

#### Worked Example

Consider the edge-weighted graph shown below

1/15/2007

• (a) determine the longest path from v1 to all other vertices in the graph

gacl

(b) if an edge (v2,v3) with weight w(v2,v3) = -4 were added, how would this affect the longest paths?

1/15/2007

19

#### Worked Example

- (a) It should be easy to see that  $s_{v1} = 0$ ,  $s_{v2} = 5$ ,  $s_{v3} = 1$ ,  $s_{v4} = 3$  (verify by applying Bellman's equations in the order (v1, v3, v4, v2)

- (b) This edge would close a cycle {v3, v4, v2}. We therefore use Liao-Wong to determine whether any change has occurred to the longest paths Examining the feedback edge (v2,v3), we see that  $s_{v3} \ge s_{v2} 4$  ( $1 \ge 5 4$ ) and therefore the extra edge has not affected the longest paths

#### Summary

- · This lecture has covered

- Edge-weighted graphs, shortest and longest path problems

- Longest path through a DAG

- Longest path through a general graph: Liao-Wong

- Longest path as a LP

- This brings us to the end of our "theory break". Next lecture will look at scheduling digital circuits.

| 1/15/2007 | Lecture8 | gac1 | 21 | 1/15/2007 | Lecture8 | gacl | 22 |

|-----------|----------|------|----|-----------|----------|------|----|

|           |          |      |    |           |          |      |    |

|           |          |      |    |           |          |      |    |

#### Suggested Problems

- Find the *shortest* path through the DAG used as an example in this lecture (\*)

- Try to apply the Liao-Wong algorithm to find the shortest path through the cyclic graph example. Does it work? If not, why not? (\*\*\*)

- In the cyclic example, change the weight of edge (v3,v0) to -4. Now apply Liao-Wong to the *shortest* path problem. (\*)

#### ASAP and ALAP scheduling

- We're now entering the final portion of the course

- Scheduling and retiming

- Resource sharing algorithms

- Floorplanning

- Function Approximation

- Perspectives for the future

- · This lecture covers

- The ASAP scheduling algorithm

- The ALAP scheduling algorithm and operation slack

- Introducing timing constraints into schedules

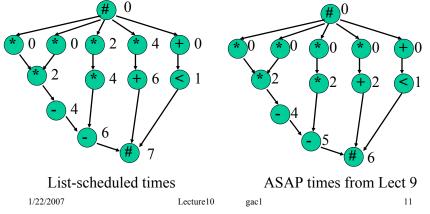

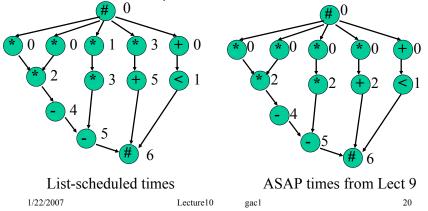

#### **ASAP Scheduling**

- The simplest type of scheduling occurs when we wish to optimize the overall latency of the computation and do not care about the number of resources required

- This can be achieved by simply starting each operation in a CDFG as soon as its predecessors have completed

- This strategy gives rise to the name ASAP for "As Soon As Possible"

| 1/22/2007 | Lecture9 gac1 | 1 | 1/22/2007 | Lecture9 gac1 | 2 |

|-----------|---------------|---|-----------|---------------|---|

|           |               |   |           |               |   |

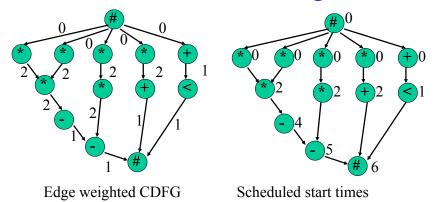

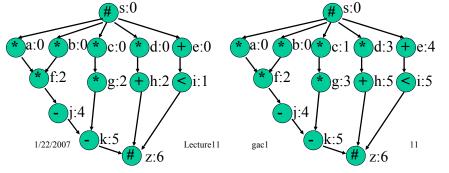

#### ASAP Scheduling

- Let's label each edge in the CDFG with the latency of the node producing that edge

- Then scheduling under ASAP is equivalent to finding the longest path between each operation and the source node

- Since a CDFG is a DAG, we can use the DAG longest path algorithm presented in Lecture 8

- Consider the original example from Lecture 1, and assume that multiplication takes two cycles, whereas addition and comparison take one cycle

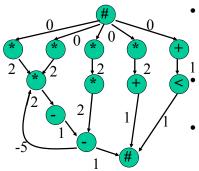

**ASAP Scheduling**

Applying the DFG algorithm to finding the longest path between the start and end nodes leads to the scheduled start times on the right-hand diagram

3

1/22/2007

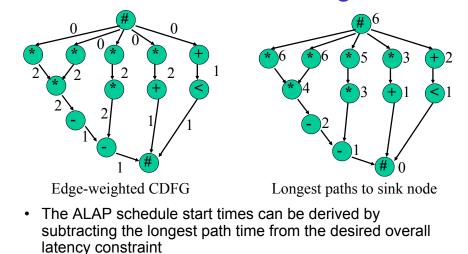

#### **ALAP Scheduling**

- The ASAP algorithm schedules each operation at the earliest opportunity. Given an overall latency constraint, it is equally possible to schedule operations at the latest opportunity.

- This leads to the concept of As-Late-As-Possible (ALAP) scheduling.

- ALAP scheduling can be performed by seeking the longest path between each operation and the end or "sink" node.

- We will re-examine the example, under the same delay assumptions, with an overall latency constraint of 6 clock cycles.

#### ALAP Scheduling

#### ALAP Scheduling

Here are the ALAP start times. You can see that each operation starts at the latest opportunity possible to still meet 6 cycles overall

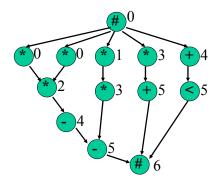

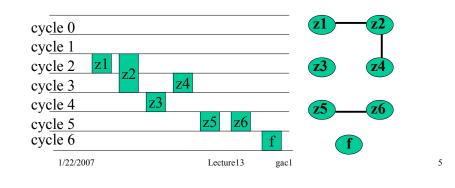

#### **Mobility**

gac 1

• Let's compare the ASAP and ALAP schedules:

• The highlighted nodes have equal ASAP and ALAP times. For all others there is a difference of at least once cycle.

gac1

Lecture9

7

1/22/2007

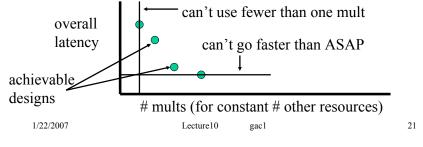

#### Mobility

- The difference between the ALAP and ASAP times for an operation is called the *operation mobility* or *slack*.

- Mobility measures how free we are to move the operation into different time-slots.

- Operations with zero mobility are *critical operations*, and together form the *critical path*, which determines how fast our circuit will run.

- More sophisticated scheduling algorithms will take advantage of positive mobility to balance the resource requirements over time.

| 1/22/2007 | Lecture9 | gacl | 9 | 1/22 |

|-----------|----------|------|---|------|

|           |          |      |   |      |

### **Types of Timing Constraint**

- As well as an overall latency constraint, other types of timing constraint are important

- Consider these examples [DeMicheli94]

- A circuit reads data from a bus, performs a computation, and writes the result back onto the bus. The bus interface specifies that the data must be written exactly three cycles after the read

- A circuit has two independent streams of operations, constrained to communicate simultaneously to external circuits by providing two pieces of data at two interfaces. The cycle in which the data are made available is irrelevant, although the simultaneity of the data is essential.

```

/22/2007

```

```

Lecture9 gac1

```

10

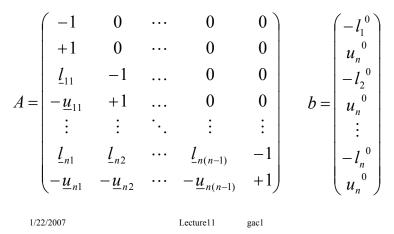

#### Types of Timing Constraint

- · We will consider two types of constraint

- a minimum timing constraint  $I_{ij}$  between operations  $v_i$  and  $v_i$ :  $S(v_i) \ge S(v_i) + I_{ij}$

- a maximum timing constraint  $u_{ij}$  between operations  $v_i$  and  $v_i : S(v_i) \le S(v_i) + u_{ii}$

- These constraints are sufficient to model the situations on the previous slide, in addition to many others. Solutions for previous slide:

- set both min and max of 3 cycles between read and write

- set both min and max of 0 cycles between the two writes

### Modelling Timing Constraints

- How can we incorporate these timing constraints within our sequencing graph-based model, and how do they affect the schedule?

- From the sequencing graph G(V,E), we construct an edge-weighted *constraint graph* G<sub>C</sub>(V,E<sub>C</sub>), where E ⊂ E<sub>C</sub>:

- the edge weights for edges in *E* are the same as before (i.e. the delay of the node producing that edge)

- we add extra edges to model the timing constraints

#### **Modelling Timing Constraints**

• Minimum timing constraints can simply be modelled by adding an extra edge  $(V_i, V_j)$  with weight  $I_{ii}$

By adding the curved edge with weight 5, the subtraction operation cannot start for at least 5 cycles after the multiplication starts

#### **Modelling Timing Constraints**

Maximum timing constraints can be modelled by adding an extra edge (V<sub>i</sub>, V<sub>i</sub>) with weight -U<sub>ii</sub>

- Now the multiplication cannot occur before -5 cycles after the subtraction starts

2 (aut) > 2 (aut) = 5 i.e.

- S(mult)  $\geq$  S(sub) 5, i.e. S(sub)  $\leq$  S(mult) + 5

- The subtraction cannot occur later than five cycles after the multiplication starts

| 1/22/2007 |  |

|-----------|--|

Lecture9

ture9 gac1

1/22/2007

Lecture9 gac1

14

#### Scheduling with timing constraints

- ASAP / ALAP scheduling can still be performed on constraint graphs through the longest path technique, BUT...

- the graph may no longer be a DAG (e.g. on the previous slide)

- we may need to use Liao-Wong to find the longest path

#### Summary

- This lecture has covered

- The ASAP scheduling algorithm

- The ALAP scheduling algorithm and operation slack

- Introducing timing constraints into schedules

- Next lecture will look at list scheduling, an heuristic method to find a short schedule given constraints on the number of each type of resource available

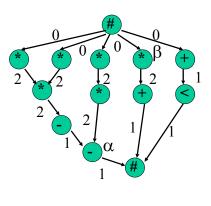

#### Suggested Problem

• Consider again the differential equation example from Lecture 1, repeated again below.

- It is required that the subtraction operation marked (α) begin no later than 3 cycles after the multiplication operation marked (β)

- Compare the ALAP

schedules with and without

this constraint

#### More Suggested Problems

• DeMicheli, Chapter 5, Problems 2 and 3 (note that DeMicheli refers to a combined min and max constraint between the source vertex and an operation as a "release time" constraint)

| 1/22/2007 | Lecture9 gac1 | 17 | 1/22/2007 | Lecture9 gac1 | 18 |

|-----------|---------------|----|-----------|---------------|----|

|           |               |    |           |               |    |

#### **List Scheduling**

- The final portion of the course covers

- Scheduling and retiming

- Resource sharing algorithms

- Floorplanning

- Function Approximation

- Perspectives for the future

- This lecture covers

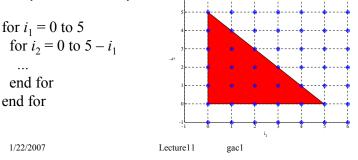

- resource constrained scheduling and latency constrained scheduling

- the resource-constrained list-scheduling algorithm

- the latency-constrained list-scheduling algorithm

```