Convertisseur analogique-numérique (CAN)

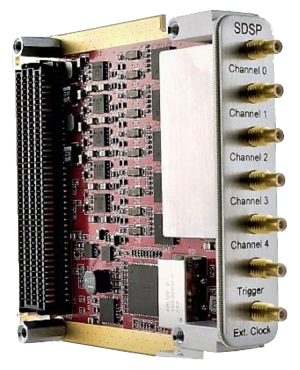

Figure 1 : Exemple d'un module FMC avec 5 canaux CAN fonctionnant chacun jusqu'à 500 MS/s avec une plage dynamique de 16 bits.

(Gracieuseté de Sundance DSP Inc., www.sundancedsp.com)

Figure 1 : Exemple d'un module FMC

avec 5 canaux CAN fonctionnant chacun jusqu'à 500 MS/s avec une plage dynamique de 16 bits.

(Gracieuseté de Sundance DSP Inc.,

www.sundancedsp.com)

Convertisseur analogique-numérique (CAN)

Analogue-to-Digital Converter don't operate continuously, but sample the analogue signal at diskrete intervals Ts= 1/ fs and convert the sampled signal to digital form.

analogique-numérique

analogique-numérique

de « poursuite »

successives

analogique-numérique

Théorème d'échantillonnage de Nyquist-Shannon

Pour bien échantillonner un signal analogique en valeurs discrètes, la fréquence d’échantillonnage doit être plus grande que le double de la fréquence maximale fmax contenue dans ce signal. La fréquence minimale d’échantillonnage fs qui permet de reconstruire le signal d’origine est connue comme la fréquence de Nyquist-Shannon.

Une fréquence inférieure à fs cause un repliement du spectre. Par exemple pour une onde en sinus, si la fréquence d’échantillonnage fs est correctement ajustée, les échantillons successifs seront pris à l’intérieure d’un même cycle du sinus et donneront donc une bonne approximation de son évolution. Par contre, si fs est inférieur à 2 fois la fréquence du signal, certains des échantillons successifs pourraient être pris dans des cycles différents causant une indétermination.

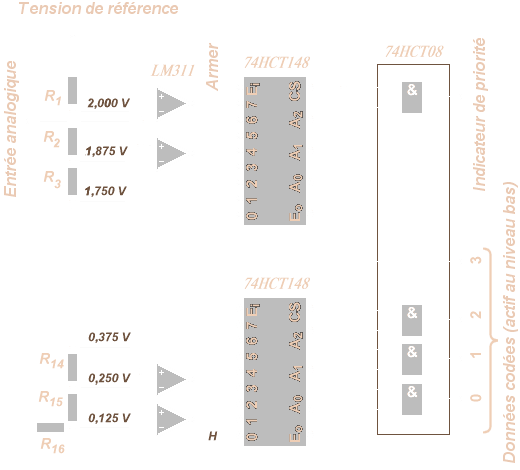

Convertisseur parallèle (dit Flash)

Figure 2 : Diagramme d’un convertisseur parallèle (Flash) de 4 bits comportant15 comparateurs

Figure 2 : Diagramme d’un convertisseur parallèle (Flash) de 4 bits comportant15 comparateurs

Figure 2 : Diagramme d’un convertisseur parallèle (Flash) de 4 bits comportant15 comparateurs

Les convertisseurs parallèles (flash en anglais) sont les plus rapides. Le principe est de produire 2N-1 tensions analogiques au moyen de 2N diviseurs de tensions qui alimentent 2N -1 comparateurs parallèles. Un bloc logique combinatoire relié à ces comparateurs donnera le résultat codé sur N bits en parallèle. Les convertisseurs Flash ont des temps de conversion inférieurs à la microseconde mais une précision assez faible (de l'ordre de la dizaine de bits). Ces convertisseurs sont souvent très chers et nécessitent une grande puissance. Par exemple, un convertisseur analogique analogique-numérique Maxim MAX104 de 8 bits utilisant un convertisseur parallèle de l’ordre de la nanoseconde nécessite 255 comparateurs et coûte environ 900 € en 2012.

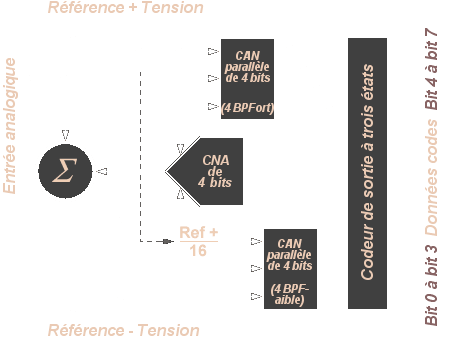

Convertisseur semi-parallèle (semi-flash)

Figure 3 : Principe d’un convertisseur semi-parallèle de 8 bits

Figure 3 : Principe d’un convertisseur semi-parallèle de 8 bits

Figure 3 : Principe d’un convertisseur semi-parallèle de 8 bits

Les convertisseurs semi-parallèles divisent le travail en deux étapes ce qui réduit le coût et la complexité au dépend d’une vitesse de conversion légèrement inférieure. Chaque convertisseur pilote un convertisseur numérique-analogique dont la sortie est soustraite au signal analogique d'entrée. L'étage suivant code le résultat de la différence, améliorant ainsi la précision finale. Un convertisseur semi-flash effectue l'ensemble des opérations en un seul cycle d'horloge, ce qui limite sa vitesse au temps de propagation total le long de la chaîne.

Dans la figure 3, le convertisseur semi-parallèle utilise 30 comparateurs pour obtenir une précision de 8 bits. Il aurait fallu 25 530 comparateurs dans un convertisseur parallèle complet.

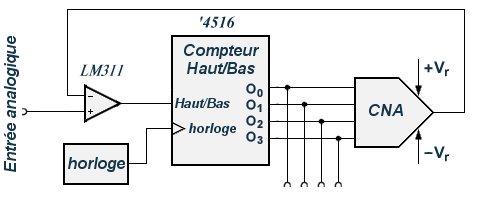

CAN de « poursuite »

Figure 4 : Principe d’un CAN de 4 bits de « poursuite »

Figure 4 : Principe d’un CAN de 4 bits de « poursuite »

Figure 4 : Principe d’un CAN de 4 bits de « poursuite »

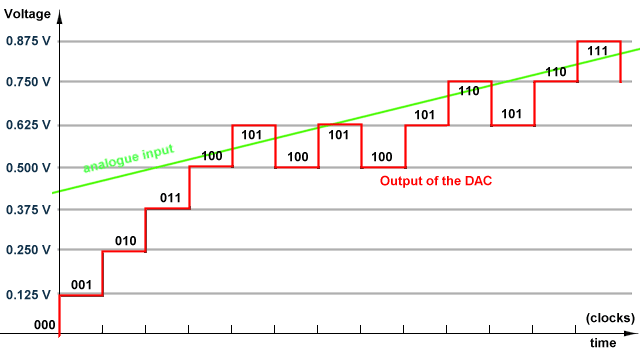

Le convertisseur de « poursuite » est une de nombreuses techniques qui utilisent un convertisseur numérique à analogique (CNA) dans une boucle à rétroaction négative. Le principe est de suivre la progression de l’amplitude du signal d’entrée à mesure qu’il est introduit dans le convertisseur. Lorsque le signal analogique commence, une première approximation numérique est effectuée et comparée par rétroaction au signal. Quand la sortie du CNA est inférieure à l’intensité du signal d’entrée, l’interrupteur Haut/Bas est en position haute et le compteur ajoute une unité. À l’inverse si le CNA est supérieur à l’entrée, le compteur diminue d’une unité.

La valeur du mot numérique augmente jusqu’à ce qu’il ait rejoint la valeur du signal réel mais seulement après un certain nombre d’itérations (un par battement de l’horloge interne) pendant lequel l’amplitude de ce signal a changé (figure 5). Par la suite, le convertisseur réagit aux variations de l’amplitude du signal analogique.

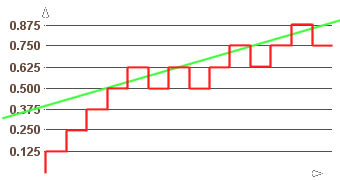

Figure 5 : Principe du comptage dans un convertisseur de « poursuite »

Cette « poursuite » introduit donc un délai entre la conversion et le signal analogue. Cette méthode n’est donc applicable que pour un signal dont les variations d’amplitude sont lentes car il faut 2n battements de l’horloge interne pour que le convertisseur puisse s’ajuster.

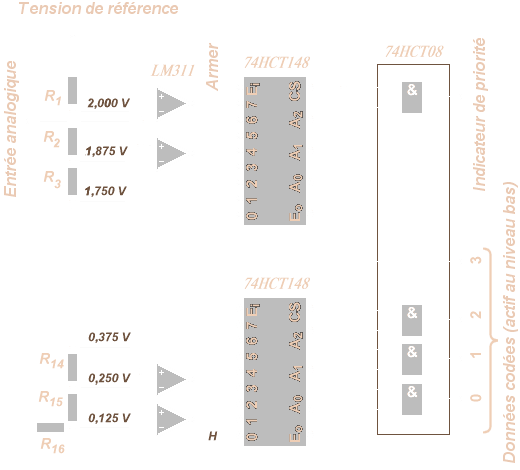

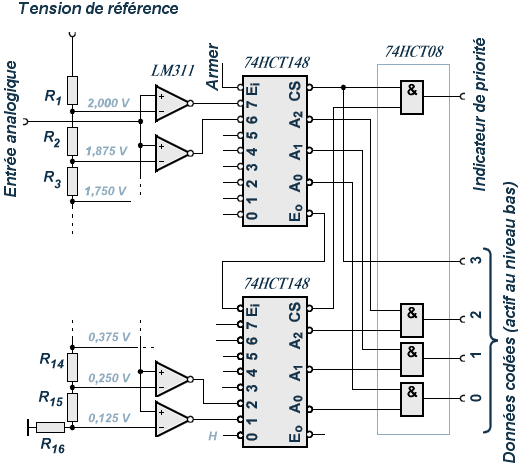

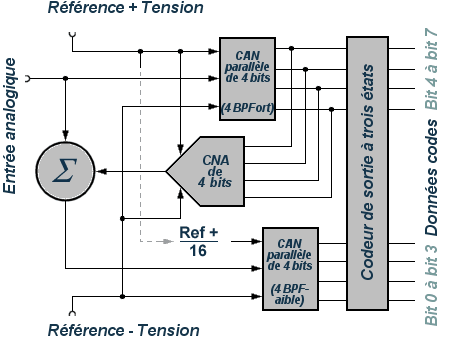

Convertisseur à approximations successives (SAR- CNA)

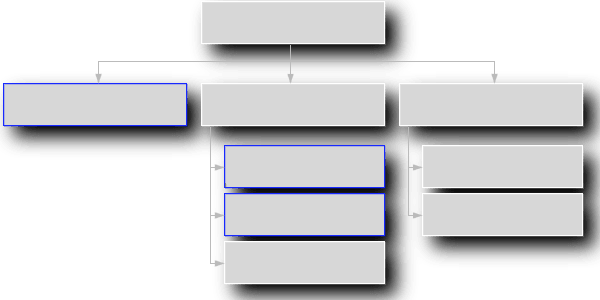

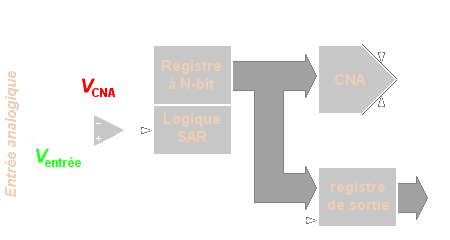

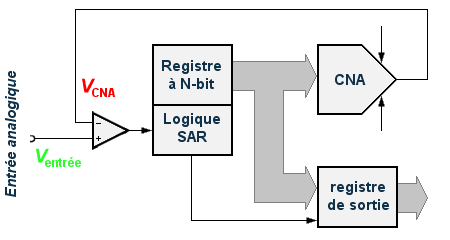

Figure 7 : Principe du SAR du CNA

Figure 7 : Principe du SAR du CNA

Figure 7 : Principe du SAR du CNA

Même s’il existe plusieurs variantes du convertisseur à approximation successives, le principe de base en est le même: un séquenceur (généralement nommé SAR pour Successive Approximation Register), couplé à un convertisseur numérique-analogique (CNA), produit une tension analogique, qui est comparée au signal à convertir. Le résultat de cette comparaison se poursuit itérativement en allant du bit le plus significatif (ou bit de poids fort BPFort) à celui de moindre signification (ou bit de poids fort BPFaible) jusqu’à la correspondance la plus parfaite possible entre le mot numérique et le signal d’entrée.

Dans cet algorithme, la valeur du bit le plus significatif d’un registre à N bits est d’abord mis à 1 (c’est à-dire 100 … 0,00). Cela donne une valeur analogue de sortie du CNA de Vr /2, où Vr est la tension de référence d’entrée du convertisseur analogue-numérique.

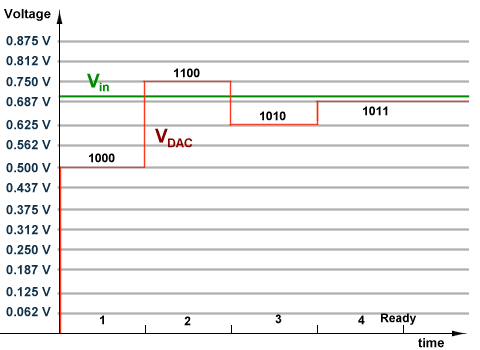

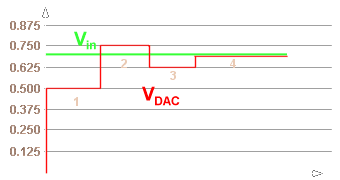

Figure 6 : Opération SAR (exemple d’un convertisseur analogue-numérique de 4 bits)

(VDAC = VCNA; Vin = Ventrée)

Figure 6 : Opération SAR (exemple d’un convertisseur analogue-numérique de 4 bits)

(VDAC = VCNA; Vin = Ventrée)

Cette valeur (VCNA) est comparée à Ventrée :

- si elle est inférieure, la valeur du bit le plus significatif est logiquement correct (Vr /2 est inférieur à Ventrée) et demeure à « 1 » ;

- si elle est supérieure, c’est que la valeur de la tension du bit le plus significatif est trop grande et il est remis à « 0 ».

L’algorithme passe ensuite au bit suivant qu’il met à « 1 ». La comparaison est refaite avec Ventrée sur ce second bit. Le tout se répète jusqu’à ce que l’algorithme ait passé tous les bits.